# Efficient Online Path Profiling

*A Thesis submitted for the degree of

**Doctor of Philosophy**

in the Faculty of Engineering*

by

**Kapil Vaswani**

Department of Computer Science & Automation

Indian Institute of Science

Bangalore, India

October, 2007

*Dedicated to*

**my beloved parents**

# Efficient Online Path Profiling

Submitted for the degree of Doctor of Philosophy

September 2007

## Abstract

Most dynamic program analysis techniques such as profile-driven compiler optimizations, software testing and runtime property checking infer program properties by *profiling* one or more executions of a program. Unfortunately, program profiling does not come for free. For example, even the most efficient techniques for profiling *acyclic, intra-procedural paths* can slow down program execution by a factor of 2. In this thesis, we propose techniques that significantly lower the overheads of profiling paths, enabling the use of path-based dynamic analyzes in cost-sensitive environments.

*Preferential path profiling* (PPP) is a novel software-only path profiling scheme that efficiently profiles given subsets of paths, which we refer to as *interesting* paths. The algorithm is based on the observation that most consumers of path profiles are only interested in profiling a small set of paths known a priori. Our algorithm can be viewed as a generalization of the Ball-Larus path profiling algorithm. Whereas the Ball-Larus algorithm assigns weights to the edges of a given CFG such that the sum of the weights of the edges along each path through the CFG is unique, our algorithm assigns weights to the edges such that the sum of the weights along the edges of interesting paths is unique. Furthermore, our algorithm attempts to achieve a minimal and compact encoding of the interesting paths; such an encoding significantly reduces the overheads of path profiling by eliminating expensive hash operations during profiling. Interestingly, we find that both the Ball-Larus algorithm and PPP are essentially a form of arithmetic coding. We use this connection to prove that the numbering produced by PPP is optimal.

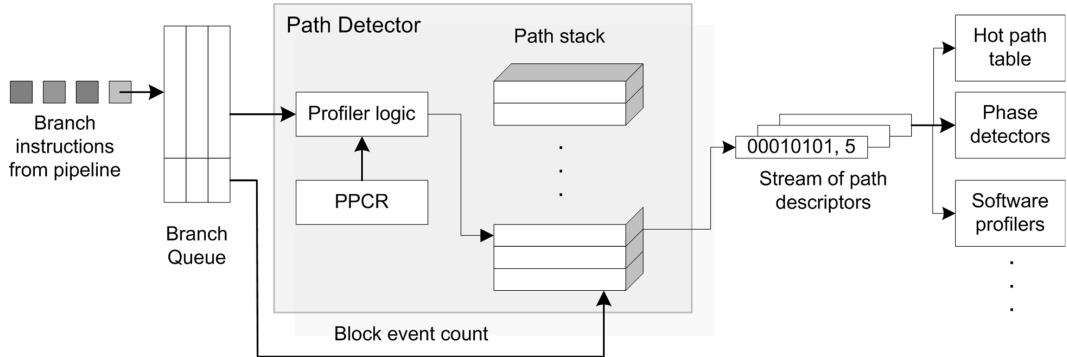

We also propose a programmable, non-intrusive *hardware path profiler* (HPP). The hardware profiler consists of a path detector that detects paths by monitoring the stream of retiring branch instructions emanating from the processor pipeline. The path detector can be programmed to detect various types of paths and track architectural events that occur along paths. The second component of the hardware profiling infrastructure is a Hot Path Table (HPT), that collects accurate hot path profiles.

Our experimental evaluation shows that PPP reduces the overheads of profiling paths to 15% on average (with a maximum of 26%). The algorithm can be easily extended to profile inter-procedural paths at minimal additional overheads (average of 26%). We modeled HPP using a cycle-accurate superscalar processor simulator and find that HPP generates accurate path profiles at extremely low overheads (0.6% on average) with a

moderate hardware budget. We also evaluated the use of PPP and HPP in a realistic profiling scenarios. We find that the profiles generated by HPP can effectively replace expensive profiles used in profile-driven optimizations. We also find that even well-tested programs tend to exercise a large number of untested paths in the field, emphasizing the need for efficient profiling schemes that can be deployed in production environments.

# Declaration

**Copyright © 2007 by Kapil Vaswani.**

“The copyright of this thesis rests with the author. No quotations from it should be published without the author’s prior written consent and information derived from it should be acknowledged”.

# Acknowledgments

It gives me great pleasure to acknowledge faculty, colleagues and friends who have contributed immensely to this thesis and to four eventful years at the Indian Institute of Science. First and foremost, I would like to acknowledge my advisors, Prof. Y. N. Srikant and Prof. Matthew Jacob, for their extraordinary guidance, inspiration and steadfast support through these years. Under their guidance, I found the freedom to express myself without inhibitions and explore my interests. The depth and foresight in their thought processes was exemplary. Working with them has been an absolute honour.

I would also like to acknowledge P. J. Joseph, my colleague at the Department of Computer Science and Automation, who was instrumental in shaping my thoughts and my research over these years. I am grateful to him for volumes of technical advise that he was ever so forthcoming with during our discussions and for his inspirational and calming presence. I would like to acknowledge my co-researcher Aditya Thakur for his critical contributions to the thesis. I thoroughly enjoyed my interactions with him in reading group meetings and discussions over a cup of coffee. Working and collaborating with him was a truly enriching experience.

I am extremely grateful to Aditya Nori, Trishul Chilimbi and Sriram Rajamani, researchers at Microsoft Research. They brought a fresh perspective to the problems we collaborated on and were never short of support and encouragement. I learnt a great deal from the way they approached problems, their persistence, and their attention to detail. I also thank Michael Bond for his help with the Scale compiler and Microsoft's Phoenix compiler team for their assistance with the path profiler implementation. I also thank Prof. Chiranjib Bhattacharya, Prof. Sirish Shevade, Prof. Priti Shankar and Prof. Govindarajan for their technical inputs.

I owe a great deal to my colleagues Anand Vardhan, Sujit and Bharath Kumar for creating a pleasant and enriching environment at the Compiler lab. Their presence, co-operation and advise went a long way in ensuring an enjoyable stay at IISc. I am also thankful to Mr. Pushparaj, scientific officer at the Department of CSA for his help in setting up some of the computational facilities, without which much of our research would not have been possible. I sincerely thank the staff at the Department of CSA, including Mr. George Fernandes and Mrs. Lalitha for handling the plethora of administrative matters

ever so efficiently.

I would also like to acknowledge my friends Neerav Abani and Joseph Viathara for their company through the years. Finally, I owe a great deal to my parents and my brother Nikhil for being extremely patient and supportive in difficult times and for having trusted and encouraged me through the years. They have and will continue to be role models for me.

# Contents

|                                                                  |     |

|------------------------------------------------------------------|-----|

| <b>Abstract</b>                                                  | iii |

| <b>Declaration</b>                                               | v   |

| <b>Acknowledgments</b>                                           | vi  |

| <b>1 Introduction</b>                                            | 1   |

| 1.1 Automated program analysis . . . . .                         | 3   |

| 1.2 Efficiency of dynamic program analysis . . . . .             | 6   |

| 1.3 Path profiling . . . . .                                     | 7   |

| 1.4 Contributions of the thesis . . . . .                        | 8   |

| 1.5 Organization of the thesis . . . . .                         | 10  |

| <b>2 Literature Survey</b>                                       | 11  |

| 2.1 Software path profiling . . . . .                            | 11  |

| 2.2 Hardware profiling . . . . .                                 | 13  |

| 2.3 Applications of path profiling . . . . .                     | 14  |

| 2.3.1 Profile-guided Optimizations . . . . .                     | 14  |

| 2.3.2 Software debugging and testing . . . . .                   | 17  |

| 2.3.3 Computer architecture . . . . .                            | 18  |

| <b>3 Preferential Path Profiling</b>                             | 19  |

| 3.1 Introduction . . . . .                                       | 19  |

| 3.2 Preliminaries . . . . .                                      | 20  |

| 3.2.1 Definitions . . . . .                                      | 20  |

| 3.2.2 Ball-Larus Profiling . . . . .                             | 21  |

| 3.2.3 An illustrative example . . . . .                          | 23  |

| 3.3 Preferential Path Profiling . . . . .                        | 24  |

| 3.3.1 The Preferential Path Profiling Algorithm . . . . .        | 27  |

| 3.3.2 Example . . . . .                                          | 31  |

| 3.3.3 Discussion . . . . .                                       | 33  |

| 3.4 Interprocedural Preferential Path Profiling (IPPP) . . . . . | 33  |

---

|          |                                                               |           |

|----------|---------------------------------------------------------------|-----------|

| 3.4.1    | Preliminary Definitions . . . . .                             | 34        |

| 3.4.2    | Specifying Interesting IPSs . . . . .                         | 34        |

| 3.4.3    | Profiling Interesting IPSs . . . . .                          | 35        |

| 3.4.4    | IPPP Algorithm . . . . .                                      | 36        |

| 3.4.5    | Avoiding Inlining through Code Duplication . . . . .          | 37        |

| 3.4.6    | Discussion . . . . .                                          | 39        |

| 3.5      | Residual Path Profiling (RPP) . . . . .                       | 39        |

| 3.5.1    | Intra-procedural Residual Path Profiling . . . . .            | 39        |

| 3.5.2    | Inter-procedural Residual Path Profiling . . . . .            | 40        |

| 3.5.3    | Discussion . . . . .                                          | 41        |

| 3.6      | Experimental evaluation . . . . .                             | 41        |

| 3.6.1    | Inter-procedural Preferential Path Profiling (IPPP) . . . . . | 45        |

| 3.6.2    | Intra-procedural Residual Path Profiling . . . . .            | 45        |

| 3.6.3    | Inter-procedural Residual Path Profiling . . . . .            | 48        |

| 3.6.4    | Residual Path Profiling Simulation . . . . .                  | 49        |

| 3.6.5    | Code Size Increase . . . . .                                  | 49        |

| <b>4</b> | <b>Path Profiling - an information theoretic perspective</b>  | <b>51</b> |

| 4.1      | Arithmetic Coding . . . . .                                   | 51        |

| 4.2      | The Ball-Larus algorithm and Arithmetic coding . . . . .      | 53        |

| 4.2.1    | The PPP algorithm and Arithmetic Coding . . . . .             | 56        |

| 4.3      | Analysis of the PPP algorithm . . . . .                       | 57        |

| <b>5</b> | <b>A Programmable Hardware Path Profiler</b>                  | <b>60</b> |

| 5.1      | Introduction . . . . .                                        | 60        |

| 5.2      | Representing and Detecting Paths in Hardware . . . . .        | 63        |

| 5.3      | Associating architectural metrics with paths . . . . .        | 67        |

| 5.4      | Collecting Hot Path Profiles . . . . .                        | 69        |

| 5.5      | Experimental Evaluation . . . . .                             | 71        |

| 5.5.1    | Experimental Methodology . . . . .                            | 72        |

| 5.5.2    | Quality of Hardware Path Profiles . . . . .                   | 72        |

| 5.5.3    | Profiling Overheads . . . . .                                 | 76        |

| <b>6</b> | <b>Conclusions and Future Work</b>                            | <b>78</b> |

| 6.1      | Conclusions . . . . .                                         | 78        |

| 6.2      | Future directions . . . . .                                   | 79        |

| 6.2.1    | Algorithmic extensions . . . . .                              | 79        |

| 6.2.2    | Applications of PPP . . . . .                                 | 80        |

| 6.2.3    | Applications of HPP . . . . .                                 | 80        |

# List of Figures

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

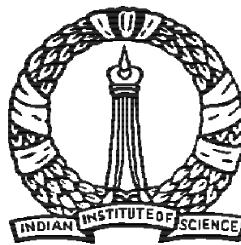

| 1.1 | Overview of automated tools and techniques for analyzing performance and correctness of programs. . . . .                                                                                                                                                                                                                                                                                                                                          | 2  |

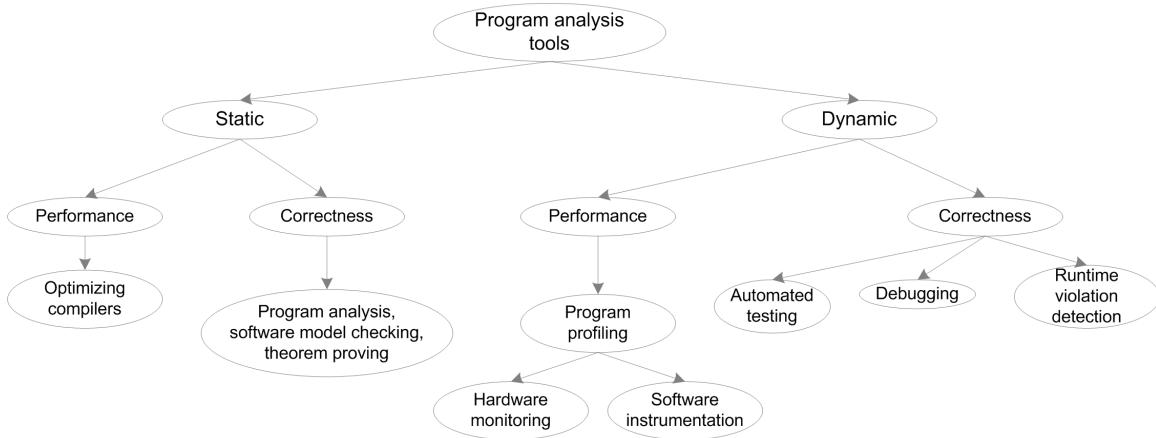

| 1.2 | Overview of <code>compile-profile-recompile</code> cycle that generates binaries tuned to a specific program behavior. . . . .                                                                                                                                                                                                                                                                                                                     | 4  |

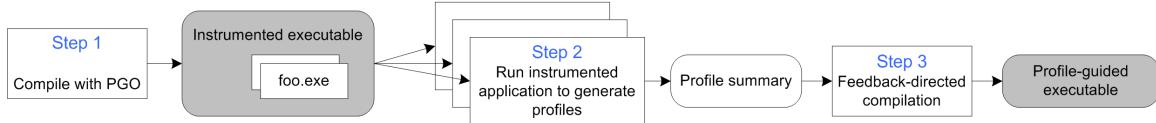

| 1.3 | Trade-off between information content and profiling overheads for various control flow profiling techniques. . . . .                                                                                                                                                                                                                                                                                                                               | 6  |

| 1.4 | Acyclic, intra-procedural paths through a control flow graph. . . . .                                                                                                                                                                                                                                                                                                                                                                              | 7  |

| 2.1 | A scenario where an edge profile may not accurately reflect control flow behavior. If blocks ABC are candidates for superblock scheduling, the edge BY is a side exit. From the edge profile, it is not clear how often the blocks ABC are likely to complete. The frequency with which the side exit is taken lies between 0 and 500. . . . .                                                                                                     | 15 |

| 2.2 | A control flow graph illustrating the loss in precision due to the conservative nature of data flow analysis. In (a), the dataflow fact $X=2$ holds at the exit of node A but not at the exit of B. Due to the merge, the analysis conservatively assumes that the dataflow fact does not hold at the entry of C. Figure (b) shows the version of the graph after splitting the merge. Here, the fact $X=2$ holds at the entry of node C'. . . . . | 17 |

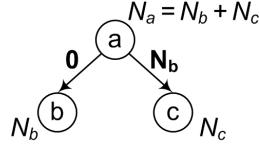

| 3.1 | The Ball-Larus Algorithm. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                  | 21 |

| 3.2 | Assignment of weights to edges using the Ball-Larus algorithm . . . . .                                                                                                                                                                                                                                                                                                                                                                            | 22 |

| 3.3 | Computing the Ball-Larus identifier of a path from an edge assignment. . . . .                                                                                                                                                                                                                                                                                                                                                                     | 22 |

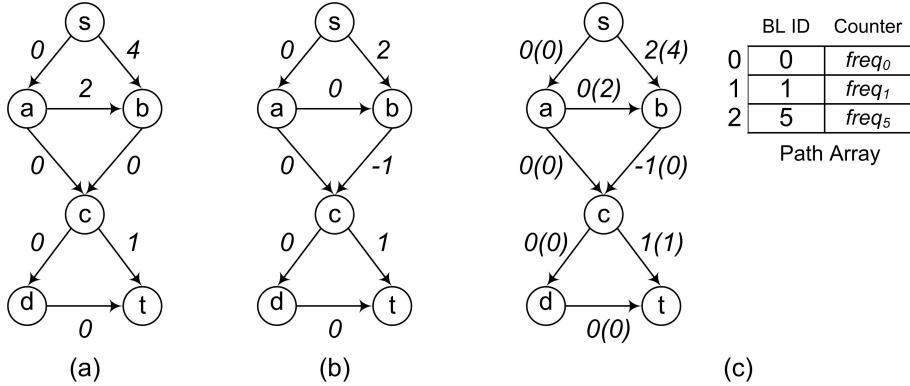

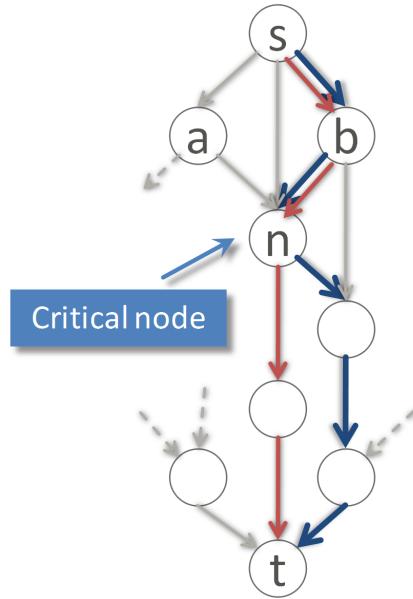

| 3.4 | Motivating example for PPP. (a) A DAG $G$ with 6 paths with edges numbered using the Ball-Larus algorithm. (b) $G$ with edges having only PPP assigned numbers for three interesting paths $I = \{sacd, sact, sbct\}$ . (c) $G$ with edges assigned two numbers, a PPP number and a Ball-Larus number (in parenthesis). The path array is accessed using the PPP counter. . . . .                                                                  | 23 |

| 3.5 | A counterexample for separation of paths. . . . .                                                                                                                                                                                                                                                                                                                                                                                                  | 25 |

| 3.6 | A counterexample for perfect edge assignment. . . . .                                                                                                                                                                                                                                                                                                                                                                                              | 26 |

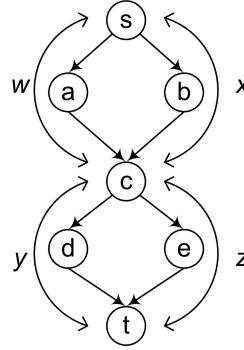

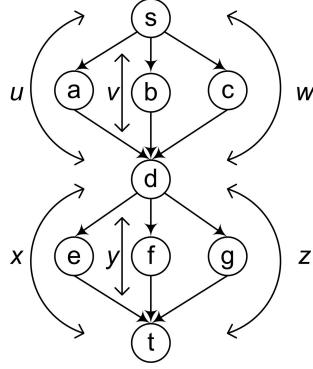

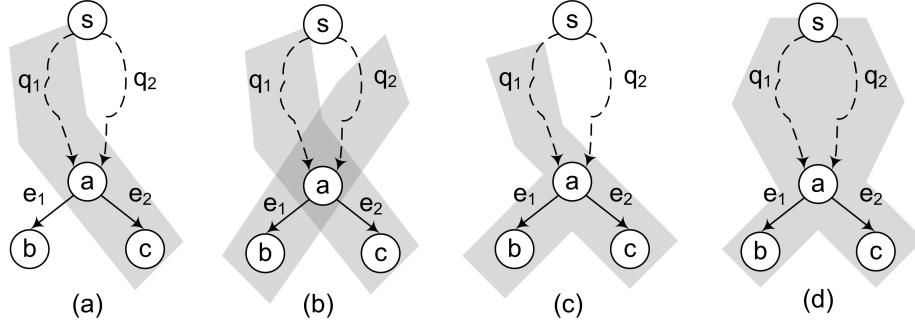

| 3.7 | Critical nodes for pairs of paths. . . . .                                                                                                                                                                                                                                                                                                                                                                                                         | 28 |

---

|      |                                                                                                                                                                                                                                                                                                                                       |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.8  | The assignment of weights to edges under four scenarios . . . . .                                                                                                                                                                                                                                                                     | 30 |

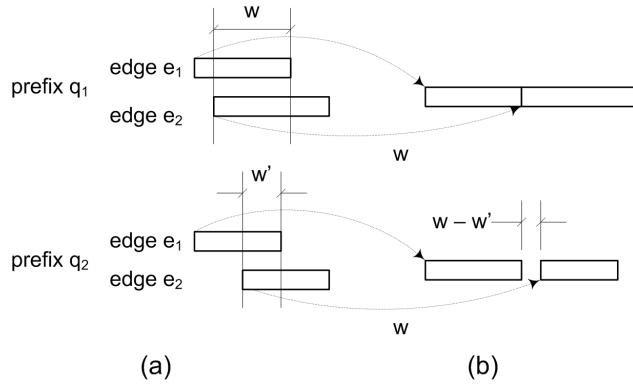

| 3.9  | The effect of using the <i>join</i> operator to conservatively assign weights to edges. (a) Intervals induced by the prefixes before the join, and (b) effective intervals after the join. . . . .                                                                                                                                    | 30 |

| 3.10 | The preferential path profiling (PPP) algorithm for computing an edge assignment for a set of interesting paths. . . . .                                                                                                                                                                                                              | 32 |

| 3.11 | Figure illustrating a scenario in which PPP assigns a sub-optimal numbering but an optimal numbering clearly exists. . . . .                                                                                                                                                                                                          | 34 |

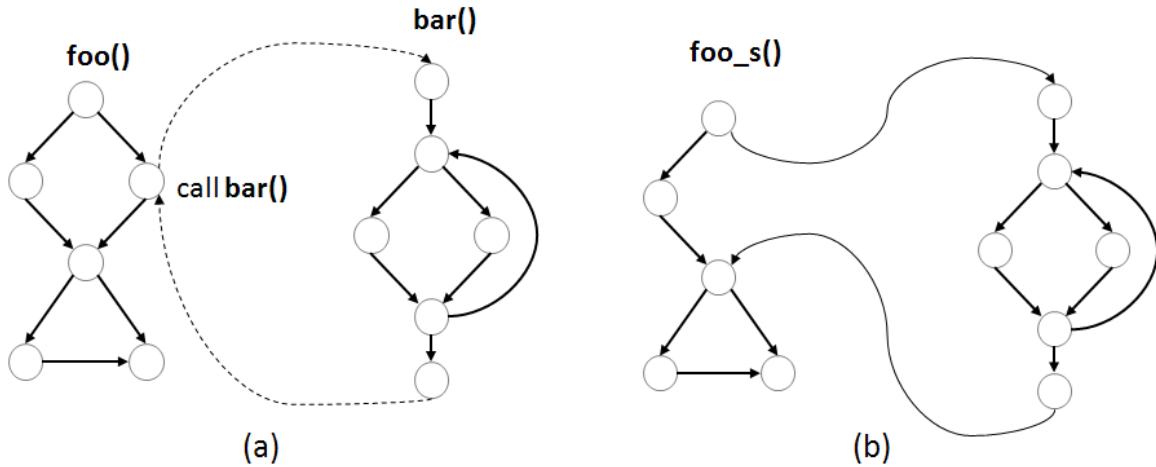

| 3.12 | IPPP example. (a) Interesting inter-procedural path originating <i>infoo()</i> , passes through the function <i>bar()</i> , before returning to <i>foo()</i> . (b) After function inlining, this path becomes an intra-procedural path in the super-graph <i>foo_s()</i> . . . . .                                                    | 35 |

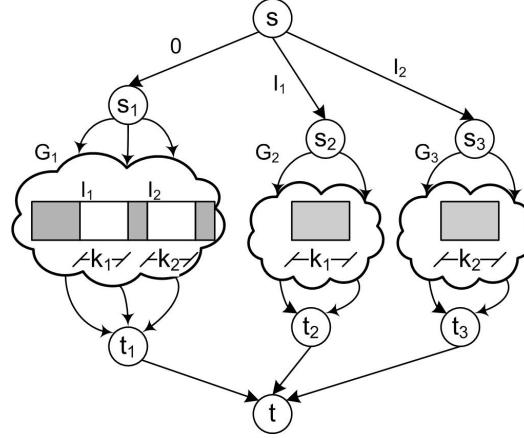

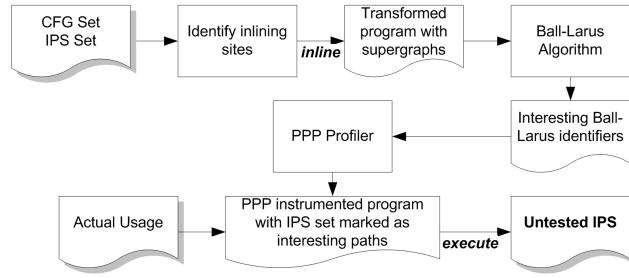

| 3.13 | Overview of the inter-procedural preferential path profiling scheme. . . . .                                                                                                                                                                                                                                                          | 37 |

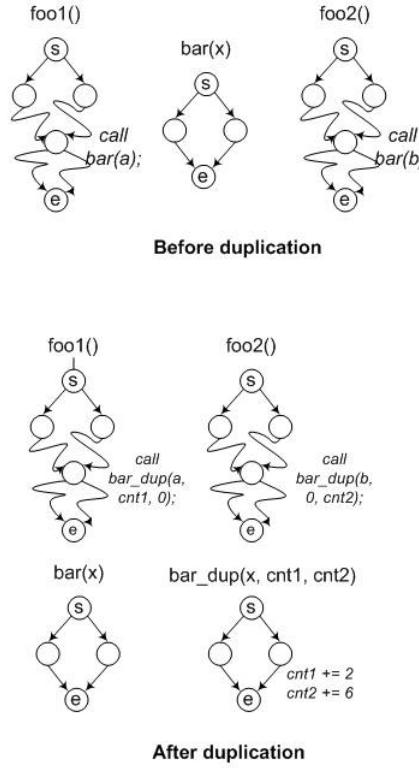

| 3.14 | An example that illustrates an IPPP approach based on function replication that avoids increase in code size due to inlining-based IPPP. . . . .                                                                                                                                                                                      | 38 |

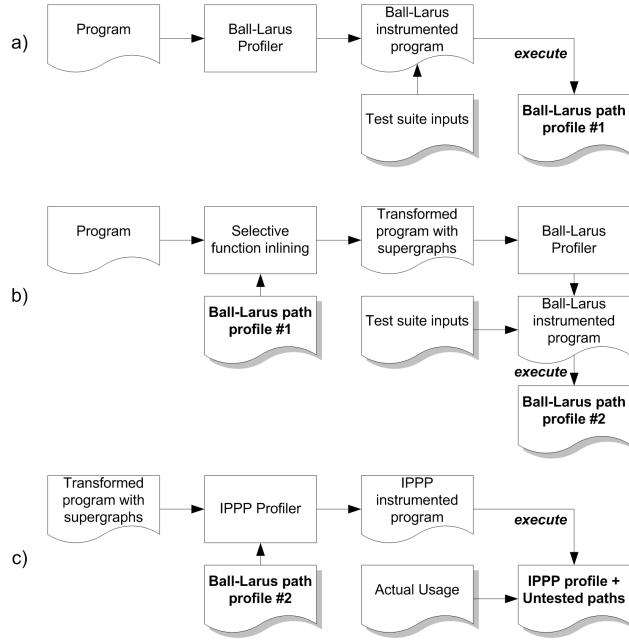

| 3.15 | Residual path profiling for IPPPs. (a) Profile executed paths on test suite inputs using the Ball-Larus scheme. (b) Inline functions to convert executed IPSs to intra-procedural paths and re-execute on test inputs. (c) Use path profile from (b) to drive PPP and run program with field inputs to detect untested paths. . . . . | 40 |

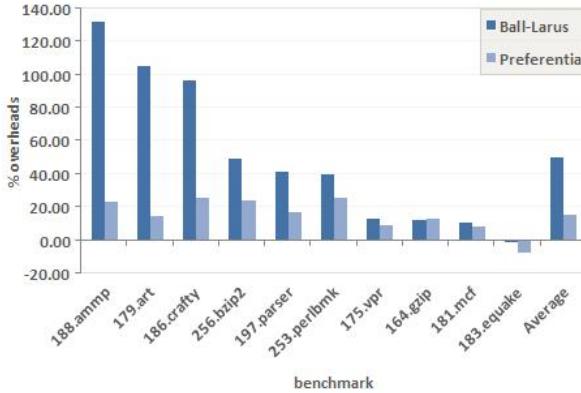

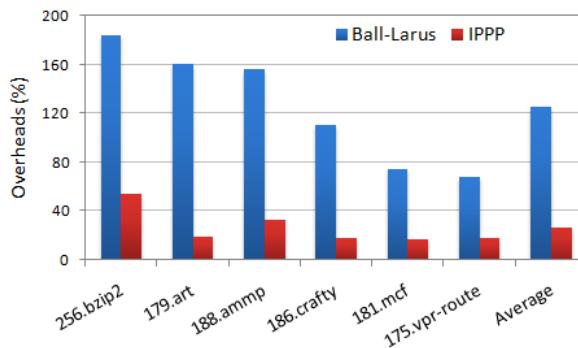

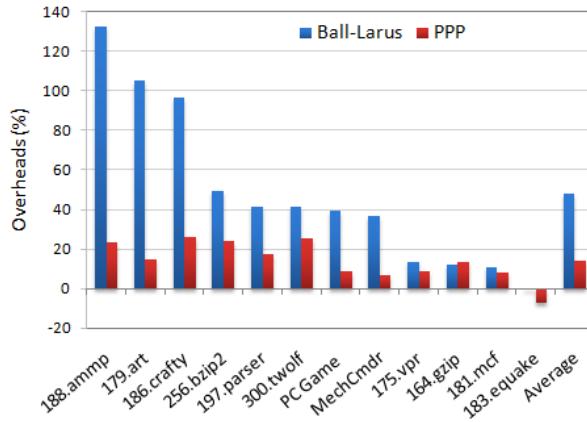

| 3.16 | Overheads of preferential path profiling. . . . .                                                                                                                                                                                                                                                                                     | 43 |

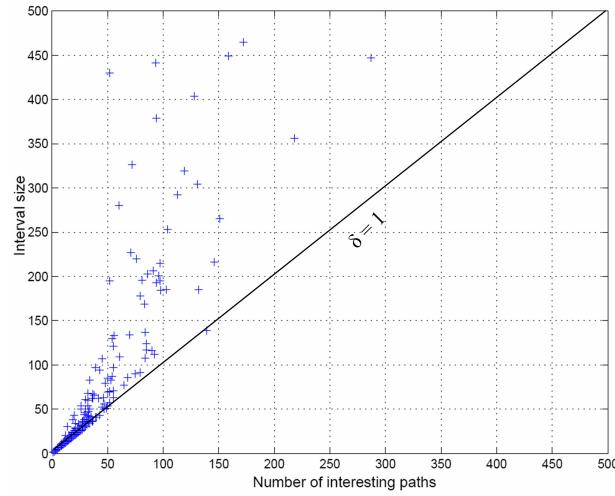

| 3.17 | $\delta$ values achieved by preferential path profiling. . . . .                                                                                                                                                                                                                                                                      | 44 |

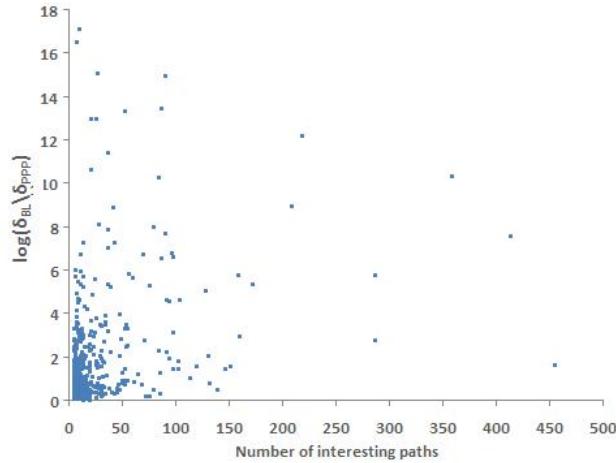

| 3.18 | Ratio of the $\delta$ values obtained using the Ball-Larus algorithm and PPP (on a log scale). . . . .                                                                                                                                                                                                                                | 44 |

| 3.19 | Runtime overheads of inter-procedural path profiling. . . . .                                                                                                                                                                                                                                                                         | 45 |

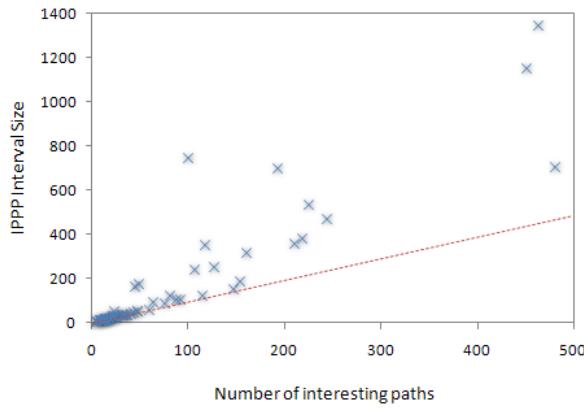

| 3.20 | Compact numbering achieved by IPPP for several functions from programs in the SPEC CPU2000 suite. . . . .                                                                                                                                                                                                                             | 47 |

| 3.21 | Comparison of runtime overheads of Ball-Larus and intra-procedural RPP. .                                                                                                                                                                                                                                                             | 47 |

| 4.1  | The Ball-Larus algorithm as a model computation process. . . . .                                                                                                                                                                                                                                                                      | 54 |

| 4.2  | Example for the procedure <i>computeBLModel</i> . . . . .                                                                                                                                                                                                                                                                             | 55 |

| 4.3  | The coding algorithm that takes a model $D$ and path $p \in paths(G)$ as input, and returns the path identifier or the encoding for $p$ . . . . .                                                                                                                                                                                     | 56 |

| 5.1  | Components of the Hardware Path Profiling Infrastructure. . . . .                                                                                                                                                                                                                                                                     | 61 |

---

|                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

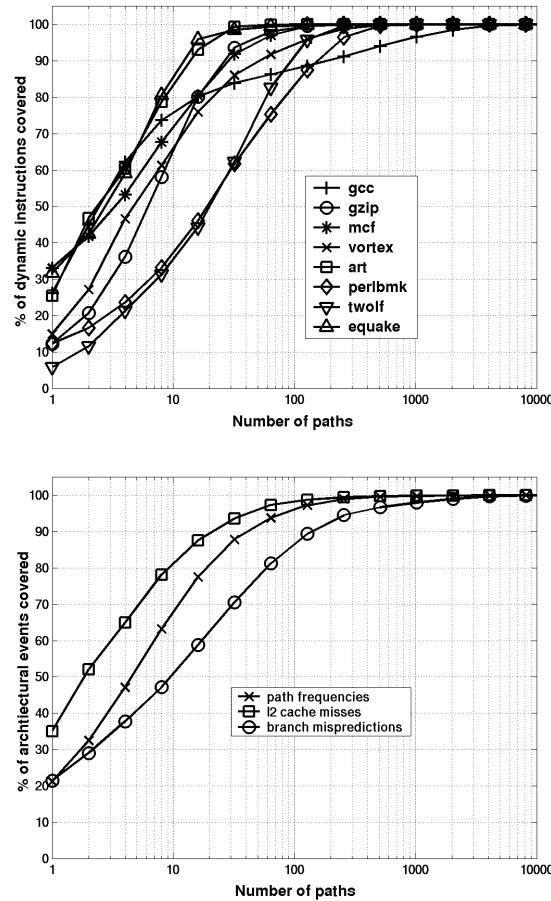

| 5.2 (a) Cumulative distribution of dynamic instructions along acyclic, intra-procedural paths. (b) Average cumulative distribution of path frequencies, L2 cache misses and branch mis-predictions along paths. The top 100 paths account for more than 80% of the dynamic instructions and a high percentage of L2 cache misses and branch mis-predictions in the SPEC CPU2000 programs studied. . . . . | 62 |

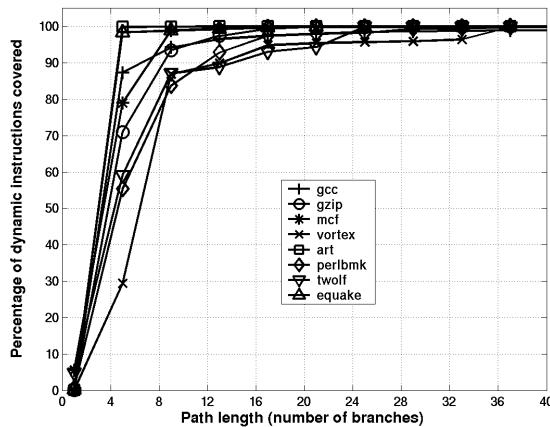

| 5.3 Distribution of dynamic instructions according to the length of Ball-Larus paths they execute along. Paths with at most 16 branches account for over 90% of program execution in most programs. . . . .                                                                                                                                                                                               | 63 |

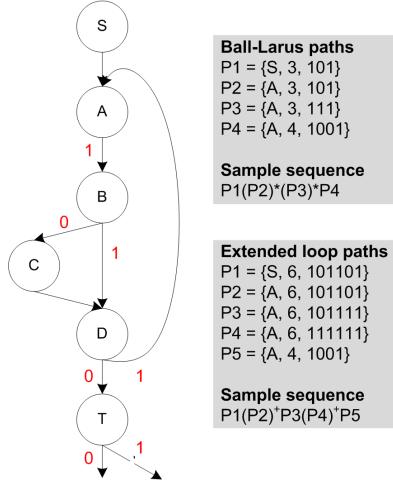

| 5.4 The control flow graph, path descriptors and a sequence of Ball-Larus paths and extended loop paths detected for a sample execution of a procedure. Blocks S and C do not end with branches and block A ends with an unconditional jump to B. All other blocks end with conditional branches. . . . .                                                                                                 | 65 |

| 5.5 (a) A power model that computes power consumption in L1 dcache and (b) corresponding apportioning logic that assigns costs to instructions that simultaneously access L1 dcache. Here, both <i>dcache_access_power</i> and <i>dcache_access_cost</i> are computed a priori; these are constants for a specific process technology. . . . .                                                            | 66 |

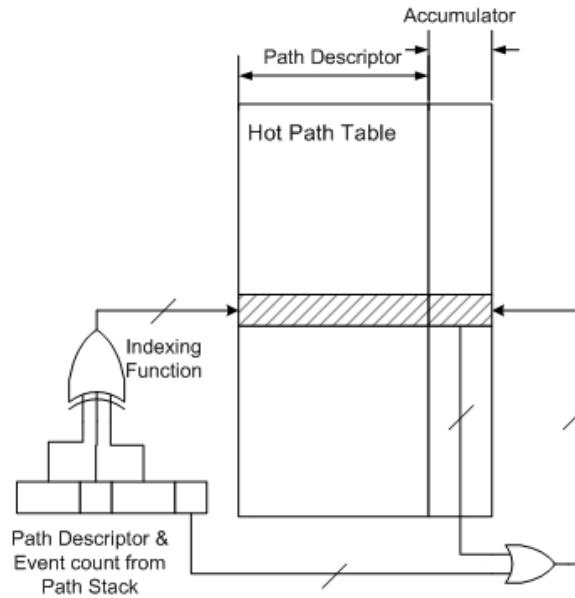

| 5.6 The Hot Path Table that collects hot path profiles. The HPT is indexed using bits from the incoming path's address, length and branch outcomes. . . . .                                                                                                                                                                                                                                               | 70 |

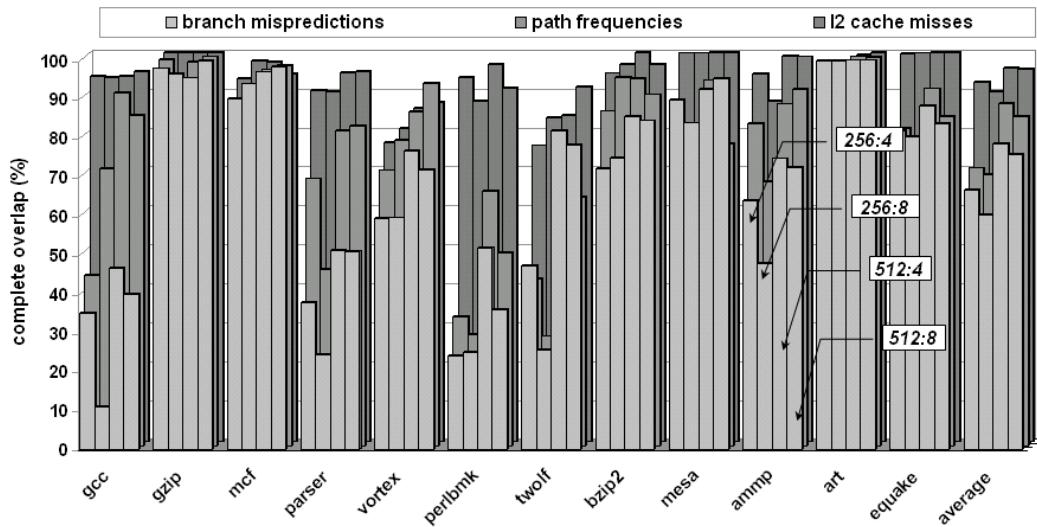

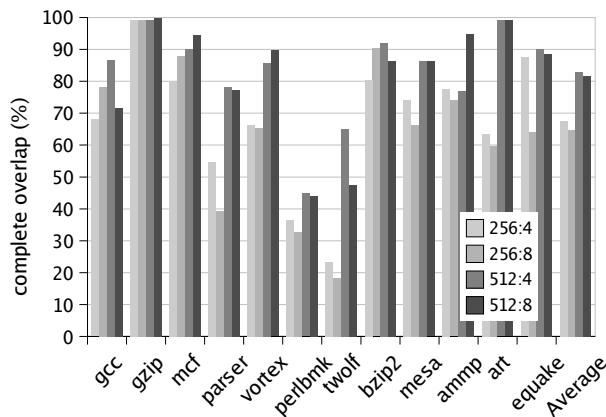

| 5.7 Complete overlap percentages for various profiler configurations when profiling path frequencies, L2 cache misses and branch mis-predictions. . . . .                                                                                                                                                                                                                                                 | 73 |

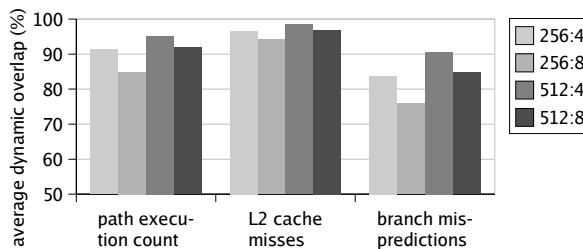

| 5.8 Average dynamic overlap percentages for various profiler configurations when profiling path frequencies, L2 cache misses and branch mis-predictions. . . . .                                                                                                                                                                                                                                          | 74 |

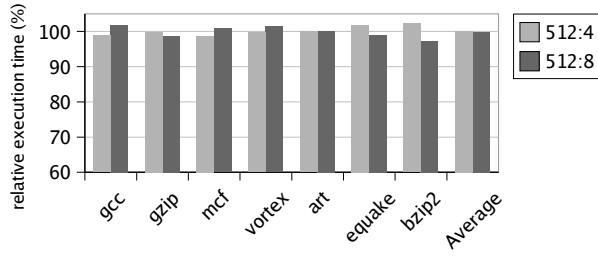

| 5.9 Execution times of binaries superblock-scheduled using path profiles from two HPT configurations normalized against the execution time of a binary scheduled using a complete path profile. . . . .                                                                                                                                                                                                   | 75 |

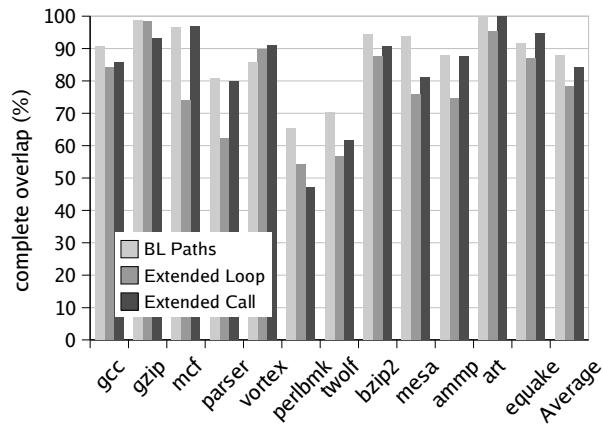

| 5.10 Accuracy of complete extended path profiles collected using the hardware path profiler. Paths extend across one backward branch/procedure call. . . . .                                                                                                                                                                                                                                              | 75 |

| 5.11 Accuracy of complete path-wise power profiles for various HPT configurations, obtained using an analytical model for power consumption in the cache hierarchy. . . . .                                                                                                                                                                                                                               | 76 |

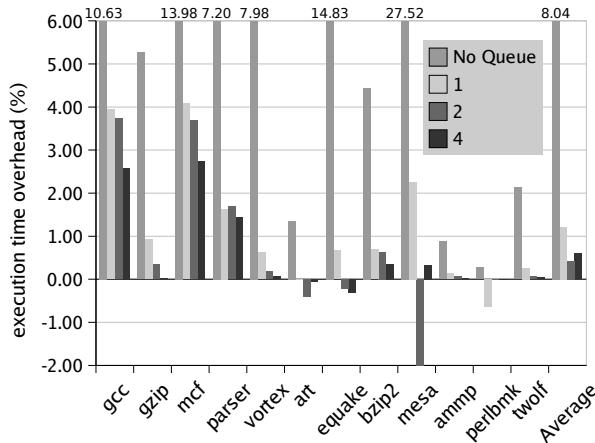

| 5.12 Execution time overheads incurred due to the hardware profiler while profiling BL paths for various branch queue sizes. . . . .                                                                                                                                                                                                                                                                      | 77 |

# List of Tables

|     |                                                                                                                                                                                      |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Untested intra-procedural path information obtained from residual path profiling. . . . .                                                                                            | 46 |

| 3.2 | Untested IPS information obtained from inter-procedural residual path profiling. . . . .                                                                                             | 48 |

| 3.3 | Untested intra-procedural path information obtained using a more robust test suite. . . . .                                                                                          | 49 |

| 3.4 | Increase in code size due to Ball-Larus and PPP intra-procedural profiling. . . . .                                                                                                  | 50 |

| 3.5 | Increase in code size due to Ball-Larus and inter-procedural path profiling. . . . .                                                                                                 | 50 |

| 4.1 | A sample probability model for the alphabet $\Sigma = \{a, b, c, d, e, !\}$ . . . . .                                                                                                | 52 |

| 4.2 | The Ball-Larus probability model $D_G$ for the graph $G$ computed by <i>computeBLModel</i> . . . . .                                                                                 | 55 |

| 4.3 | The PPP probability model $D_G$ for the graph $G$ computed by <i>computePP-PIncrements</i> . . . . .                                                                                 | 58 |

| 5.1 | Branch type–profiler operation mapping for detecting Ball-Larus paths . . . . .                                                                                                      | 65 |

| 5.2 | Branch type–Profiler operation mapping for detecting paths for a Whole Program Path. . . . .                                                                                         | 66 |

| 5.3 | Baseline Processor Model . . . . .                                                                                                                                                   | 70 |

| 5.4 | Parameters considered during experiments based on Plackett-Burman design to determine an effective HPT configuration. The corresponding low and high values are also listed. . . . . | 71 |

"To measure is to know"

## Chapter 1

---

*Lord Kelvin*

# Introduction

We are in the midst of a computing revolution. Our lives are increasingly dependent on computing systems that range from tiny mobile devices to large data centers that drive the internet. Ideally, we would like to ensure that the systems we use and rely so heavily on are provably correct, reliable, cost-effective and deliver high performance. However, this is rarely the case in practice. Systems deployed in the real world break down frequently despite rigorous design, development and testing procedures. And performance remains a real concern despite significant advances in processor technology.

This apparent fragility of modern-day systems can be attributed to the ever-increasing size and complexity of both hardware and software components. Not long ago, most applications were designed to solve relatively simpler problems, were developed from scratch by small teams of expert programmers and ran on relatively simple hardware. Consequently, it was possible for programmers to reason about both the correctness and performance of most parts of the system. This is rarely the case with systems we build today. Software applications routinely span several million lines of code. These applications are typically composed from a large number of distributed components written in different languages and developed simultaneously by geographically distributed teams of programmers. Very often, programmers are expected to maintain and extend large and unfamiliar code bases. The hardware that runs these applications is equally complex with multiple cores, complex memory, network and I/O subsystems being the norm.

One of the primary reasons why programmers can build software systems at such a large scale is the presence of several layers of abstraction in the programming stack. For instance, programming models such as object-oriented programming and aspect oriented programming allow programmers to write code at a higher level of abstraction. Such programming models also simplify the use of libraries and off-the-shelf components, enabling large-scale reuse of software. Virtual-machine based execution adds several other layers of abstraction, enabling features such as architecture-independence, runtime optimizations, automatic memory management and memory safety via type checking and process

Figure 1.1: Overview of automated tools and techniques for analyzing performance and correctness of programs.

isolation. Microprocessor vendors have used the Instruction Set Architecture (ISA) as another layer of abstraction to improve processor performance while maintaining backward compatibility. The ISA, which defines aspects such as the instructions supported by the processor, the native data types, number of architectural registers etc, serves as the external interface of a processor family. Processor architects are free to change the processor micro-architecture (i.e. the implementation of the ISA) as long as the micro-architecture adheres to the ISA. This layer of abstraction has enabled several micro-architectural optimizations such as caching and speculative execution and has even allowed architects to change the internal model of execution via techniques such as out-of-order execution.

While these layers of abstraction are critical to the process of designing large scale software systems, they have an unwarranted side-effect. These layers introduce a disconnect between the programmer's view of the system and the code that eventually runs on the hardware. This disconnect makes it virtually impossible for programmers to manually reason about a system's performance, and to a certain extent, about its correctness. Consider for instance the use of off-the-shelf libraries. A library is typically associated with an external interface and implicit rules that govern the use of the library. Unless these rules are explicitly stated and interpreted correctly, a programmer could unintentionally introduce a bug by not conforming to the rules. The use of libraries also makes it harder for programmers to identify and alleviate performance bottlenecks since the bottlenecks may lie deep within the library code. Similarly, the use of OO features, JIT compilation, garbage collection and micro-architectural optimizations such as multi-level caches, speculation and out-of-order execution also add to the complexity of reasoning about an application's performance.

## 1.1 Automated program analysis

One way of bridging the divide between the programmer’s and the machine’s view of an application is through automated program analysis tools. Ideally, such tools should automatically (a) identify parts of an application that perform sub-optimally, infer the reasons behind the sub-optimal performance and suggest possible solutions to alleviate performance anomalies, and (b) detect whether an application meets a given correctness criteria, identify the *root cause* of any violations and if possible, suggest a suitable fix. It is now widely recognized that such tools are critical to the development of large scale computing systems and their design continues to be an area of active research (see Figure 1.1 for a classification of some of the commonly used program analysis tools).

There exist two fundamentally different approaches to the design of automatic program analysis tools. **Static program analysis** methods infer program properties simply by analyzing the program’s source code. For example, compilers can statically detect and eliminate redundant expressions using data flow analysis. Similarly, a software model checker can detect whether a program violates a given safety property by building an abstract model of the program from its source code. On the other hand, **dynamic program analysis** techniques infer program properties by *monitoring* the program during one or more of its executions. A program’s execution may be monitored by injecting probes into the program (instrumentation), via dedicated hardware or by observing the program’s response to a set of inputs.

Because of this difference in approach to program analysis, static and dynamic techniques exhibit different characteristics. Static analysis techniques can infer *stronger* program properties i.e. properties valid across all inputs to the program. For instance, a compiler flags an expression as redundant only if the expression is redundant along all paths from program entry to the statement containing the expression. Similarly, a static verification tool certifies a program to be correct only if the correctness criteria is met for all inputs. Furthermore, static analysis techniques can detect defects early in the software design cycle. On the other hand, a dynamic analysis can only prove properties based on observations made during a finite number of runs of the program. A dynamic race detection algorithm, for instance, may be able to detect the presence of a race condition in a given run of a multi-threaded program, but cannot prove that the program is race-free. For these reasons, static analysis tools are generally desirable.

Unfortunately, despite significant recent progress in the design of scalable static analysis tools, the use of automated static analysis tools has been restricted to proving simple properties of large programs or complex properties of simple programs. For example, modern compilers for languages like Java can statically detect simple forms of memory safety violations such as stack overflows even in large programs. On the other hand, static tools that analyze complex properties such as the shape of heap-allocated data structures,

Figure 1.2: Overview of *compile-profile-recompile* cycle that generates binaries tuned to a specific program behavior.

presence of races or determine the worst case execution time of a program do not scale to large programs because of the prohibitively large state space involved in the analysis. Many static analysis tools address the state space explosion problem by losing precision. For instance, most compilers prefer using imprecise and inexpensive pointer analysis algorithms, trading off compilation time with optimization opportunities. Dynamic techniques do not suffer from these deficiencies because the analysis is restricted to a small number states that occur during one or more executions of a program. Furthermore, most dynamic analysis techniques are extremely precise because they can precisely track the values of program variables at each program point, witness all state transitions and have access to information that is available only at runtime (such as the state of the heap, I/O and network requests and hardware performance metrics). It is therefore not surprising that several dynamic tools have proven successful in analyzing complex properties for large programs. We now discuss three scenarios where dynamic techniques have been employed with great success.

**Feedback-directed compiler optimizations.** Traditionally, optimizing compilers were designed as static tools that identify, and where ever possible, eliminate inefficient operations and coding errors in programs. In the static compilation model, compiler optimizations statically analyze a program's source code and eliminate inefficient operations via one or more semantics-preserving program transformations. It turns out that in most optimizations, identifying inefficient code is not always easy because both the cost of the operation and the benefit of the optimization depend on several external factors such as program input, interactions between optimizations, and the underlying micro-architecture. For instance, given a choice, it may be beneficial to optimize a piece of code that is more likely to be executed frequently rather than code that is rarely executed. Since many of these factors are inherently dynamic, static compilers are unable to resolve these cost-benefit tradeoffs, which, in turn, reduces the effectiveness of optimizations.

Feedback-directed optimizations [45] overcome these limitations by using a dynamic approach to optimizations. To employ these optimizations, programmers follow a *compile-profile-recompile* cycle (illustrated in Figure 1.2). During the first compilation step, the program is instrumented to collect information about its runtime

behavior. Next, the instrumented binary is executed using a set of *representative* inputs provided by the programmer, generating a set of *profiles* in the process, where each profile characterizes an aspect of the program’s dynamic behavior. Finally, the profiles are fed back to the compiler, which uses them to resolve cost-benefit trade-offs that occur during optimizations. In essence, the use of feedback in the form of execution profiles *biases* the optimizations towards the common case behavior of a program, resulting in highly tuned binaries. Feedback-directed optimizations are now supported by most industry-strength compilers and experience suggests that these optimizations can result in substantial performance gains.

**Software testing.** Software testing is a dynamic analysis technique that attempts to find errors by subjecting a given program to a number of inputs and checking the outputs against the expected response. Unlike static analysis, testing does not exhaustively verify correctness for all possible program inputs and hence, does not guarantee program correctness. However, it has been found that the reliability of software components is correlated with the degree of testing i.e. components tested more rigorously are less likely to fail when deployed. Testing is also preferred because it does not require a property or a specification of software artifact, both of which are hard to obtain (although the availability of either can improve testing efficiency). Furthermore, testing methods are not constrained by the size or complexity of programs being tested. Both manual and automated testing techniques have been employed for checking large programs, ranging from compilers to enterprise applications.

**Runtime invariant detection and checking.** The criteria for correctness of programs are often expressed as *invariants*. An invariant is a program property that does not change during the course of a program’s execution. For example, programmers often use assert statements to specify intended invariants; expressions in the assert statements define the set of values program variables are allowed to take. Checking whether user specified invariants are not violated along any path in the program is central to program verification. Unlike static analyzes, which try and prove invariants statically, runtime invariant checking is concerned with checking for invariant violations during program execution. This is typically achieved by placing probes at specific locations and tracking the values of program variables. For instance, the Java runtime checks for violations of the (implicit) invariant that array indices do not exceed the declared bounds. Similarly, a dynamic race detector [44] checks for violations of the invariant that all accesses to a shared memory location are ordered by the happens-before relation.

Figure 1.3: Trade-off between information content and profiling overheads for various control flow profiling techniques.

## 1.2 Efficiency of dynamic program analysis

Virtually all dynamic analysis techniques have a common characteristic - the analyzes are based on **profiling/monitoring** one or more executions of the program. Unfortunately, although significantly more efficient than static analysis, program profiling does not come for free. Depending on the nature of profile data being collected, profiling may slow down a program's execution considerably. High profiling overheads adversely effect the efficiency of dynamic analysis techniques and often preclude their use in cost-sensitive settings.

The close connection between profiling overheads and the efficiency of dynamic analysis is best illustrated by considering the class of *control flow profiling* techniques. As the name suggests, a control flow profiling technique attempts to characterize the flow of control in a program's execution by identifying parts of the program exercised in a given run, and optionally, the temporal order and frequency with which they were exercised. Figure 1.3 illustrates some of the most commonly used control-flow profiling techniques and compares their overheads. *Program tracing*, a profiling technique that generates an exhaustive trace of events that occur during a program's execution, lies on one end of the spectrum. While a trace records information in sufficient detail for any dynamic analysis technique, tracing programs is extremely expensive. Not surprisingly, the use of full program tracing has been mostly restricted to research environments. On the other end of the spectrum are a number of *point profiling* techniques, which count the frequency with which specific points in the program are exercised in a given execution. For instance, a basic block profiler tracks the number of times each basic block in the program was executed. Similarly, a call-graph profiler counts the frequency with which a function was called from each of its callers.

Point profiling techniques are simple and extremely inexpensive because collecting these profiles requires only a few additional instructions per program point. However,

Figure 1.4: Acyclic, intra-procedural paths through a control flow graph.

this increased profiling efficiency comes at the cost of a loss in precision. Point profiles are coarse abstractions of a programs control flow behavior. These profiles are *lossy* because a programs actual control flow behavior cannot be accurately recovered from a point profile. In other words, a given point profile may correspond to several executions of a program, some of which may not even be feasible. Recent research has shown that this loss in precision may reduce the efficacy of dynamic analysis techniques that use these profiles. For instance, it has been shown that profile-driven optimizations such as superblock scheduling are less effective if driven by point profiles instead of more accurate profiles. Similarly, software testing is less effective if code coverage is measured using point profiles. This trade-off is fundamental to any profiling technique and the way this trade-off is resolved has a large bearing on the efficiency of dynamic analysis techniques.

### 1.3 Path profiling

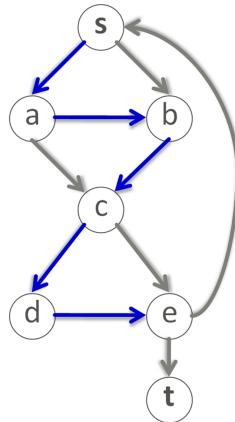

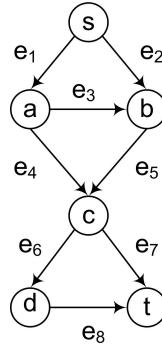

In the case of analyses that use control flow profiles, this trade-off between precision and profiling overheads can be resolved using a profiling technique known as **path profiling** (proposed by Ball and Larus [6]). A path profiler monitors the control flow of a program at the granularity of **acyclic, intra-procedural paths**. An acyclic, intra-procedural path (simply referred to as path for the rest of this article) is defined as any sequence of instructions that originates at the beginning of a procedure or a loop and terminates at the end of a procedure or at a loop back-edge. Consider the control flow graph shown in 1.4. The node **s** represents the entry node to the function and **t** represent the exit/return node. The sequence of blocks **sbcde** constitutes a path that begins and ends at a procedure boundary. Similarly, blocks **sabcde** constitute a path that terminate at a loop back-edge.

Much like a point profiler, a path profiler tracks the frequency with which each path was exercised in a given execution. Path profiles are a succinct and pragmatic abstrac-

tion of a programs dynamic control-flow behavior. Control-flow information captured by a path profile is much more precise than basic block or edge profiles. Also, path profiles are considerably smaller than complete instruction traces. Recording program paths has proved valuable in a wide variety of areas such as computer architecture, compilers, debugging, program testing, and software maintenance [5]. Several compiler optimizations perform better when trade-offs are driven by accurate path profiles [2, 20, 55]. Program paths are also a more credible way of measuring coverage of a given test suite. In addition, abstractions of paths can help automatic test generation tools generate more robust test cases. Finally, program path histories often serve as a valuable debugging aid by revealing the instruction sequence executed in the lead up to interesting program points.

While the benefits of using path profiles over point profiles are obvious, let us consider how path profilers fare on the overheads front. Our measurements of an implementation of a state-of-the-art path profiler [6] indicate an average execution time overhead of 50% with as much as a 132% overhead in the worst case and other studies report similarly high overheads [9]. Although this represents a significant reduction over whole program tracing, the overheads are already an order of magnitude more than point profiles. The overheads of profiling increase manifold if the scope of profiling is extended beyond acyclic, intra-procedural paths [30, 48]. This has limited the use of path profiles in favor of point profiles in tasks such as measuring test coverage and driving profile-guided optimizations such as code placement, inlining, unrolling, and superblock scheduling.

Apart from these traditional usage scenarios, we envisage the use of path profiling in several cost-sensitive environments. For instance, in **residual path profiling**, we are interested in determining the set of paths that a deployed program executed in the field but were not exercised during testing. This information could be used to improve and augment test suites, and if included with bug reports resulting from field failures, could help pinpoint the root cause of errors. Another scenario involves ascertaining whether paths that were identified as hot paths during testing and used to optimize the program continue to remain hot during field usage. In addition, we might want to gather detailed information about these paths, such as cache misses, page faults, and variations in execution time, without resorting to sampling techniques [39]. Finally, we might be interested in efficiently tracking a subset of paths in deployed software that meet a certain criteria, for example, paths that access safety or security critical resources, or that exercise an error prone code region. *These tasks can be performed only if paths can be profiled at low cost and high accuracy.*

## 1.4 Contributions of the thesis

In this thesis, we propose two techniques low overhead path profiling techniques namely **preferential path profiling** (PPP) [49] and **hardware path profiling** (HPP) [51] that

enable the use of path profiles in cost-sensitive environments.

PPP is a novel software-only path profiling scheme that efficiently profiles arbitrary path subsets, which we refer to as **interesting** paths. PPP is based on the observation that several consumers of path profiles rely on profiling a small subset of paths that are known *a priori*, which we refer to as *interesting paths*. Our algorithm can be viewed as a generalization of the Ball-Larus algorithm [6]. The Ball-Larus algorithm assigns weights to the edges of a given CFG such that the sum of the weights of the edges along each path through the CFG is unique. Our algorithm generalizes this notion to a subset of paths; it assigns weights to the edges such that the sum of the weights along the edges of the interesting paths is unique. Furthermore, our algorithm attempts to achieve a minimal and compact encoding of the interesting paths; such an encoding significantly reduces the overheads of path profiling by eliminating expensive hash operations during profiling. In addition, our profiling scheme separates interesting paths from other paths and is able to classify paths during program execution. The ability to classify paths is important for many scenarios such as residual path profiling. We also propose an inter-procedural extension of PPP called IPPP, which profiles paths that span across procedures [13]. Interestingly, we find that both the Ball-Larus algorithm and PPP are essentially a form of arithmetic coding [52], a technique commonly used for data compression. We use this connection to prove an optimality result for the compactness of path numbering produced by PPP.

Unlike PPP, HPP is a programmable, non-intrusive scheme that profiles paths in hardware. HPP detects paths by monitoring the stream of retiring branch instructions emanating from the processor pipeline during program execution. HPP’s path detection mechanism can be programmed to detect several types of paths and track various architectural events that occur along paths, a task hard to emulate using software path profilers. The detector generates a stream of path descriptors, each describing a path that has just executed. The second component of HPP is a *Hot Path Table* (HPT), a compact hardware structure that processes the stream of path descriptors generated by the path detector. The HPT is designed to collect accurate hot path profiles, irrespective of the type of path being profiled, the duration of profiling and the architectural metric associated with paths.

We have implemented and evaluated both path profiling schemes over a number of standard benchmark programs. Our evaluation shows that the overheads of our profiling schemes are comparable or even lower than point profiles (Figure 1.3). The two profiling schemes make for an interesting comparison. While PPP generates accurate profiles, it incurs slightly higher overheads (15% on average). HPP on the other hand requires hardware support and generates profiles with slightly lower accuracy but imposes significantly lower overheads (0.6% on average). Consequently, PPP is naturally suited for applications in software testing and invariant checking where the accuracy of profiling is critical. On

the other hand, HPP is geared towards use in online, profile-driven and micro-architectural optimizations, where the overheads of profiling are the primary concern.

## 1.5 Organization of the thesis

This rest of thesis is organized into five chapters. Chapter 2 contains a background to various hardware and software profiling schemes and illustrates their use in several dynamic analysis techniques. Chapter 3 describes the preferential path profiling algorithm, the inter-procedural version of the algorithm and its application to residual path profiling. Chapter 4 discusses the connection between path profiling and arithmetic coding and provides the proof of optimality of preferential path profiling based on this connection. Chapter 5 presents the hardware path profiling scheme. We conclude with pointers for future work in Chapter 6.

# Chapter 2

## Literature Survey

The notion of profiling paths through a program execution has always generated significant academic interest. However, the utility of path profiles in understanding and improving program behavior has been recognized only recently. This had lead to significant interest in developing efficient and scalable schemes for profiling paths. In this chapter, we discuss some of the software and hardware path profiling schemes and describe a few areas where path profiling has added significant value.

### 2.1 Software path profiling

Ball and Larus [6] first demonstrated the feasibility of obtaining path profiles in software automatically and efficiently. The proposed instrumentation-based profiling scheme splits the dynamic instruction stream into acyclic, intra-procedural sequences, also referred to as Ball-Larus (BL) paths and tracks the frequency of occurrence of each path. A detailed description of this scheme can be found in Chapter 3.

Young and Smith [56] define a path as the last  $k$  branches of the execution trace leading to an edge. They propose a scheme for profiling  $k$ -paths by first constructing a *path CFG*, where each node corresponds to a  $k$ -path in the original graph and each edge represents the last edge of the path. Although  $k$ -paths have found utility in specific compiler optimizations like superblock scheduling [55], profiling these paths is significantly more expensive than profiling Ball-Larus paths (for reasonable values of  $k$ ).

Subsequent research in path profiling has focused on alleviating two drawbacks of Ball-Larus profiling. First, path profiling does not provide information about a program's control flow across procedure and loop boundaries, limiting its utility in inter-procedural and aggressive loop optimizations. Efforts to overcome this limitation include the Whole Program Path (WPP) [30] and extended path profiling [48]. A WPP is a complete sequence of the acyclic, intra-procedural paths traversed by a program. The sequence is compressed online by generating an equivalent context free grammar, which is compactly

represented as a DAG. Despite high compression ratios, the WPP’s size and profiling overheads hinder its widespread use. Inter-procedural path profiling [33] extends Ball-Larus profiling beyond intra-procedural paths. As a compromise between Ball-Larus paths and the WPP, Tallam et al [48] propose the notion of *extended* paths – paths that extend beyond loop or procedure boundaries. They also propose a profiling scheme that reduces overheads by approximating the frequencies of extended paths from a profile of overlapping path fragments. Both these techniques have considerably higher overhead than the Ball-Larus technique (average execution time overheads for profiling extended paths are reported to be nearly 4 times the overheads of Ball-Larus path profiling).

Several researchers have proposed a variety of techniques to reduce the overhead of Ball-Larus style path profiling [3, 4, 8, 9, 25, 53], a critical factor in cost-sensitive dynamic optimization systems. Selective path profiling [3] uses a variation of Ball-Larus numbering where edges are visited in a specific order to ensure that interesting paths are assigned a unique number that is higher than the non-unique numbers assigned to other paths, while minimizing the number of counter updates needed to compute the path number. The proposed numbering scheme is a variation of the Ball-Larus numbering scheme where edges that occur along interesting paths are numbered later than other edges. However, they find that once the number of interesting paths increases beyond a small threshold, their edges covered most of the DAG and their technique offered little advantage over Ball-Larus numbering. In addition, they make no attempt to ensure that the interesting paths are compactly numbered. Instead of minimizing the number of counter updates needed to compute a path number, we optimize the compactness of numbers assigned to interesting paths. This reduces overhead by enabling the use of a path array in place of a hash table. In comparison, our compact numbering scheme is effective even when the number of interesting paths is large.

Both *targeted path profiling* [25] and *practical path profiling* [9] attempt to efficiently profile hot program paths starting from an edge profile by eliminating unneeded instrumentation. Targeted path profiling eliminates profiling cold paths by excluding cold edges and not instrumenting paths that the edge profile predicts well. It uses Ball-Larus numbering for labeling the remaining paths. Practical path profiling attempts to improve over targeted path profiling using a variety of techniques to eliminate a larger number of paths. It also performs intelligent instrumentation placement to further reduce overhead. To minimize overhead, practical path profiling may need to classify warm edges as cold and consequently could compromise the quality of the path profile. It also uses Ball-Larus numbers to uniquely identify the remaining paths.

*Structural path profiling* [53] is a lossy, online path profiling scheme that achieves lower path profiling overheads by partitioning methods into a hierarchy of nested graphs based on their loop structure. Each resulting graph has a much smaller number of paths and

can be profiled independently. For instance, in a function with a nested loop, the outer loop is profiled first. Once path profiles for the outer levels have been collected, inner level loops are profiled until the bottom level is reached. The profiling algorithm constructs a global path profile by adjusting the local profiles of the structure graphs. *Continuous path profiling* is another lossy variation of the Ball-Larus profiling scheme directed at online environments. The scheme uses a combination of full Ball-Larus instrumentation and sampling to mitigate the overheads of maintaining hash tables while path profiling. While methods are instrumented with counter update instructions as per the Ball-Larus scheme, the hash tables are updated only occasionally.

Although these path profiling schemes reduce profiling overheads without much loss in accuracy, they cause an increase in the time required to obtain representative profiles, which in turn delays the optimization process and results in fewer optimization opportunities being exploited. Moreover, it is not clear whether these schemes can be extended for profiling other varieties of paths or for profiling program binaries, as is required in binary translation/optimization systems. Our software profiling technique is orthogonal to both as it proposes a new dense numbering scheme for interesting paths that minimizes the overhead of profiling these paths. It is also more general as it can be applied to scenarios such as residual path profiling (detecting paths not exercised by a test suite), where the techniques that targeted/continuous/structured path profiling use to reduce instrumentation overheads do not apply.

## 2.2 Hardware profiling

The importance of efficient program profiling techniques in improving performance has also been recognized by computer architects. Most modern processors provide architectural support for performance monitoring, typically in the form of event counters [46, 47]. To meet the requirements of profile-guided optimizations, hardware profilers that construct approximate point profiles using information from the processor have also been proposed [15, 17, 34].

Conte et al [15] propose an approach that uses the branch handling hardware present in most commercial processors for profiling purposes. The profiler samples the branch prediction hardware using kernel mode instructions at every kernel entry point to construct weights of a Weighted Control Flow Graph. Merten et al [34] describe a mechanism that monitors instructions at the retirement stage of the processor pipeline to identify program hotspots. ProfileMe [17] is a hardware framework that profiles instructions by tracking their progress through the pipeline and collecting information about associated events. The Relational Profiling Architecture [22] provides mechanisms that allow the software to issue queries about information regarding program behavior. These queries are serviced

by profiling hardware that monitors the pipeline. Zilles and Sohi [57] suggest a solution that advocates dedicated hardware for profiling in the form of a programmable profiling co-processor that receives profile samples from the main processor, processes it and feeds it back to the main processor. Our hardware profiler subsumes existing hardware profiling schemes and has comparatively wider applicability because of its ability to collect various types of path profiles and the added ability to associate architectural metrics with program paths.

## 2.3 Applications of path profiling

Path profiles have found applications in a wide variety of dynamic program analysis techniques. While many dynamic analysis techniques have benefitted by simply using richer path profiles instead of basic block or edge profiles, several other dynamic analyzes have been formulated using paths exclusively.

### 2.3.1 Profile-guided Optimizations

Profile-guided optimizations are a special class of compiler optimizations based on the philosophy of making the common case faster. For programs, the common case is defined by behavior that a program exhibits most frequently. For example, in a banking application, depositing and withdrawing money are likely to be the most common tasks whereas opening and closing of accounts not exercised as frequently. Traditional compiler optimizations do not distinguish between the common and uncommon case and consider all parts of the program as equally important during optimizations. On the other hand, profile-guided optimizations (PGO) use program profiles generated using a set of *representative inputs* to identify the common case and optimize the common case more aggressively. Consequently, these optimizations generate highly tuned program binaries that perform significantly better for the common case.

Traditionally, compilers have relied on simple point profiles to identify the common case and drive PGO, primarily because these profiles are simple and inexpensive to collect. More recently, several researchers have shown that the effectiveness of these optimizations can increased if path profiles are used instead. We now discuss a few optimizations that are known to benefit from richer profile information.

#### Path profile-guided superblock scheduling

Instruction scheduling is a compiler optimization that reschedules instructions (typically within a basic block) such that the resulting schedule utilizes hardware resources more efficiently, hides the latency of expensive operations and has a lower latency of execution. Superblock scheduling [23] is a variant of instruction scheduling that schedules code at the

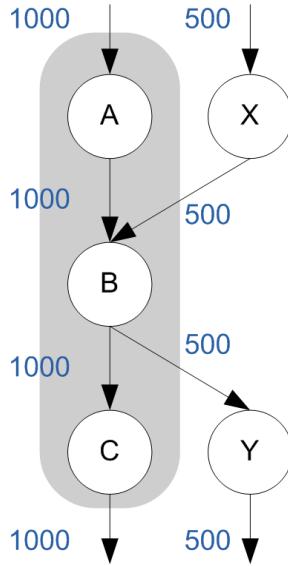

Figure 2.1: A scenario where an edge profile may not accurately reflect control flow behavior. If blocks ABC are candidates for superblock scheduling, the edge BY is a side exit. From the edge profile, it is not clear how often the blocks ABC are likely to complete. The frequency with which the side exit is taken lies between 0 and 500.

granularity of *superblocks* instead of basic blocks. A superblock is a single-entry, multiple-exit sequence of instructions with the additional characteristic that the last exit(s) (exits at the end of the superblock) are more likely to be taken than the others. In other words, once a superblock is entered, all the instructions in the superblock should be executed with high probability. In superblock scheduling, superblocks are formed using a control flow graph restructuring transformation known as *tail duplication*. Once superblocks are formed, the compiler schedules instructions in the superblock while assuming that the instructions belong to one basic block. Since the size of a superblock is typically much larger than the size of individual basic blocks, the scheduler has greater flexibility in reordering instructions, which results in better schedules. However, to compensate for the effects of reordering instructions within the superblock and ensure correctness, the scheduler inserts compensation code along edges leading to the side exits.

Traditionally, superblock formation has relied on basic block or edge profiles to identify sequences of hot basic blocks that can be transformed into superblocks. Young et al [55] show that in certain scenarios, an edge profile may not accurately reflect the control flow behavior of a program. Figure 2.1 (adapted from [55]) illustrates one such scenario. In such scenarios, the superblock scheduler will create superblocks in which control flow escapes from one of the side exits and does not reach the last exit(s) as often as expected, which reduces the benefits of scheduling. In contrast, superblocks formed using path profiles are more likely to execute to completion, making best use of the optimized schedule.

### Path-profile guided PRE

Occasionally, programmers and compiler introduce expressions whose value has already been evaluated in the program and is available for use at the statement containing the expression. Such expressions are said to be *redundant* and optimizations that detect and eliminate such expressions are an integral part of all optimizing compilers. Partial Redundancy Elimination (PRE) is an optimization that eliminates partially redundant expressions. An expression is said to be *partially redundant* if there exists a program point such that the expression is evaluated along all paths from the point to the exit (the expression is said to be *anticipable* at the program point) but the value of the expression is available only along a subset of paths from the entry to that point (the expression is *partially available* at the program point). PRE uses code hoisting to introduce instructions that evaluate the expression along paths where the expression is not redundant. This code transformation makes subsequent evaluations of the expression completely redundant and can be safely eliminated without introducing extra evaluations of the expression along any path in the program.

The traditional formulation of PRE is not applicable for expressions that are partially available and partially anticipable. This is because removing these expressions using PRE transformations as described above would introduce extra evaluations of the expression along some paths in the program. If these paths turn out to be frequently executed, the extra evaluations could slow down the program instead of improving performance. Gupta et al [20] propose a path profile-directed formulation of PRE that eliminates such expressions. The proposed approach uses path frequencies to determine the benefits of eliminating partially redundant expressions and the cost of extra evaluations introduced due to code hoisting. The optimization is performed only if the benefits exceeds the cost i.e. the cumulative frequencies of paths along with the expression is removed is higher than the frequency of paths along with an extra evaluation is introduced. A similar approach can be used to eliminate partial dead code [19].

### Precise dataflow analysis using path profiles

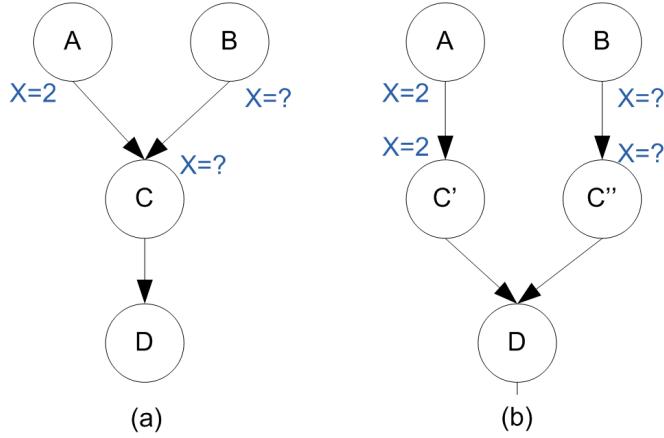

Dataflow analysis is a program analysis technique used to detect facts about program variables that hold at various points in the program. A dataflow analysis is said to be conservative if the facts computed by the analysis at a program point hold along all paths from program entry to that point. The conservative nature of dataflow analysis ensures that compiler optimizations based on the analysis are always safe. However, the safety of compiler optimizations comes at a cost. A conservative dataflow analysis is forced to loose information at join points in the program. Consider the join point in Figure 2.2. if a dataflow fact  $X = 2$  holds at the exit of node A but does not hold at the exit of node B, the analysis must conservatively assume that the the value of  $X$  is unknown at the entry

Figure 2.2: A control flow graph illustrating the loss in precision due to the conservative nature of data flow analysis. In (a), the dataflow fact  $X=2$  holds at the exit of node A but not at the exit of B. Due to the merge, the analysis conservatively assumes that the dataflow fact does not hold at the entry of C. Figure (b) shows the version of the graph after splitting the merge. Here, the fact  $X=2$  holds at the entry of node  $C'$ .

of node C. This loss in precision due to join points reduces the number of optimization opportunities and adversely effects the benefits obtained from compiler optimizations.

Ammons and Larus [2] propose an approach that improves the precision of data flow analysis by restructuring the control flow graph to eliminate join points along frequently executed paths identified using a path profile. Eliminating join points along hot paths ensures that the cost of restructuring the control flow, which involves some amount of code duplication, is more than offset by the increase in the number of optimization opportunities along these paths.

### 2.3.2 Software debugging and testing

Bugs in programs are associated with a *cause* and a *symptom* [7]. When bugs are found, either by verification tools, via in-house testing or in a deployed program, their symptoms are reported back to the programmer, typically in the form of a stack trace and a memory dump. Subsequently, much of the debugging effort is spent in finding the root cause of bugs from these symptoms, a process that involves tracing (possibly backwards) the sequence of events that lead to the symptom and identifying the sub-sequence that caused the program to transition into an invalid state. Paths are naturally suited for reasoning of this kind since paths efficiently capture a majority of event sequences that occur in a given program execution. Although existing software debuggers do not support paths explicitly, efforts have been made to make debuggers more path aware. Bruegge et al [11] propose the use of path expressions as a generic mechanism for specifying program behavior that a user wants to monitor in a debugging session. For example, the path expression `Open(Read`

+ Write)\*Close encodes the correct usage of the file API. A path-aware debugger can translate this expression into a finite-state automata, monitor the automata in parallel with the program's execution, and invoke a user-specified action if the automata reaches an error or final state. Path profiles can be used for localizing faults directly by comparing profiles obtained from correct and faulty runs and identifying paths that whose execution is highly correlated with faulty runs [41].

Paths also provide a more credible way of measuring the effectiveness of a test suite. The number of distinct paths exercised by a test suite more accurately represents the range of behaviors tested than statement or basic block coverage [14]. For this reason, paths are ideal targets for automatic test case generation tools. These tools can identify paths that are likely to cause failures and determine inputs that drive the program along these paths.

### 2.3.3 Computer architecture

Paths exhibit several interesting characteristics that can be exploited to improve processor performance. Paths exhibit *locality* - programs usually execute a small number of paths repeatedly. Furthermore, the manner in which a program exercises paths is very predictable. The locality and predictability of paths is critical to micro-architectural optimizations such as branch prediction and trace caches.