# EFFECTIVE AUTOMATIC PARALLELIZATION AND LOCALITY OPTIMIZATION USING THE POLYHEDRAL MODEL

## DISSERTATION

Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the Graduate School of The Ohio State University

By

Uday Kumar Reddy Bondhugula, B-Tech, M.S.

\* \* \* \* \*

The Ohio State University

2008

Dissertation Committee

P. Sadayappan, Adviser

Atanas Rountev

Gagan Agrawal

J. Ramanujam

Approved by

Adviser

Graduate Program in Computer Science and Engineering

#### ABSTRACT

Multicore processors have now become mainstream. The difficulty of programming these architectures to effectively tap the potential of multiple processing units is well-known. Among several ways of addressing this issue, one of the very promising and simultaneously hard approaches is automatic parallelization. This approach does not require any effort on part of the programmer in the process of parallelizing a program.

The Polyhedral model for compiler optimization is a powerful mathematical framework based on parametric linear algebra and integer linear programming. It provides an abstraction to represent nested loop computation and its data dependences using integer points in polyhedra. Complex execution-reordering, that can improve performance by parallelization as well as locality enhancement, is captured by affine transformations in the polyhedral model. With several recent advances, the polyhedral model has reached a level of maturity in various aspects – in particular, as a powerful intermediate representation for performing transformations, and code generation after transformations. However, an approach to automatically find good transformations for communication-optimized coarse-grained parallelization together with locality optimization has been a key missing link. This dissertation presents a new automatic transformation framework that solves the above problem. Our approach works by finding good affine transformations through a powerful and practical linear cost function that enables efficient tiling and fusion of sequences of arbitrarily nested loops.

This in turn allows simultaneous optimization for coarse-grained parallelism and locality. Synchronization-free parallelism and pipelined parallelism at various levels can be extracted. The framework can be targeted to different parallel architectures, like general-purpose multicores, the Cell processor, GPUs, or embedded multiprocessor SoCs.

The proposed framework has been implemented into a new end-to-end transformation tool, PLUTO, that can automatically generate parallel code from regular C program sections. Experimental results from the implemented system show significant performance improvement for single core and multicore execution over state-of-the-art research compiler frameworks as well as the best native production compilers. For several dense linear algebra kernels, code generated from Pluto beats, by a significant margin, the same kernels implemented with sequences of calls to highly-tuned libraries supplied by vendors. The system also allows empirical optimization to be performed in a much wider context than has been attempted previously. In addition, Pluto can serve as the parallel code generation backend for several high-level domain-specific languages.

#### ACKNOWLEDGMENTS

I am thankful to my adviser, P. Sadayappan, for always being very keen and enthusiastic to discuss new ideas and provide valuable feedback. He also provided me a great amount of freedom in the direction I wanted to take and this proved to be very productive for me. Nasko's (Atanas Rountev) determination in getting into the depths of a problem had a very positive influence and was helpful in making some key progresses in the theory surrounding this dissertation. In addition, I was fortunate to have Ram's (J. Ramanujam) advice from time to time that complemented everything else well. Interaction and discussions with Saday, Nasko, and Ram were very friendly and entertaining. I would also like to thank Gagan (Prof. Gagan Agrawal) for being a very helpful and accessible Graduate Studies Committee chair and agreeing to serve on my dissertation committee at short notice.

Thanks to labmates Muthu Baskaran, Jim Dinan, Tom Henretty, Brian Larkins, Kamrul, Gaurav Khanna, Sriram Krishnamoorthy, Qingda Lu, and Rajkiran Panuganti for all the interesting conversations during my stay at 474 Dreese Labs: they will be remembered. I am also thankful to the researchers at the Ohio Supercomputer Center, Ananth Devulapalli, Joseph Fernando, and Pete Wyckoff, with whom I worked during the initial stages of my Ph.D., and they gave me a good start.

Many thanks to Louis-Noël Pouchet and Albert Cohen for hosting a very pleasant visit at INRIA Saclay. Good friendships have evolved with them that will last for

a long time. I am also thankful to the group of Kathryn O'Brien at the IBM TJ Watson Research Center at Yorktown Heights – its group members Alex Eichenberger and Lakshminarayanan Renganarayana, as well as Kevin O'Brien and Dan Prener for a memorable experience during my internship there, and a mutually beneficial association. Thanks also to Nicolas Vasilache for some discussion from time to time.

I have to acknowledge the contributions of the developers of CLooG, LooPo, and PipLib, without which the theory this dissertation proposes would not have translated into a complete end-to-end system. In particular, I would like to acknowledge Cédric Bastoul for having written Cloog, and Martin Griebl and the LooPo team for creating an excellent polyhedral infrastructure over the years. I just had all the necessary components to build and complete the missing links. I hope the results presented in the thesis vindicate the efforts put into these libraries and tools both from a research and an engineering standpoint. I would also like to acknowledge the anonymous reviewers of our papers published at the International Conference on Compiler Construction 2008, and the ACM SIGPLAN conference on Programming Languages Design and Implementation 2008, for several constructive comments.

I conclude by acknowledging my parents who deserve the maximum credit for this work. My father, CDR. B. Sudhakar Reddy, and my mother, Nirmala, took extraordinary interest in my education since my childhood. I am glad their efforts have been fruitful at every stage of my studies.

## **VITA**

| Sep 10, 1982        | . Born - India                                                                                              |

|---------------------|-------------------------------------------------------------------------------------------------------------|

| Jul 2000 – Jul 2004 | Bachelor of Technology Computer Science and Engineering Indian Institute of Technology, Madras              |

| Sep 2004 – Aug 2008 | . Graduate Research Associate<br>Computer Science and Engineering<br>The Ohio State University              |

| Jun 2007 – Sep 2007 | . Research Intern Advanced Compilation Technologies IBM TJ Watson Research Labs, Yorktown Heights, New York |

| Mar 2008 – Apr 2008 | . Visiting Researcher<br>ALCHEMY team<br>INRIA Saclay, Île-de-France                                        |

## **PUBLICATIONS**

Uday Bondhugula, A. Hartono, J. Ramanujam, and P. Sadayappan. A Practical Automatic Polyhedral Parallelizer and Locality Optimizer. In *ACM SIGPLAN Programming Language Design and Implementation*, Jun 2008.

Uday Bondhugula, M. Baskaran, S. Krishnamoorthy, J. Ramanujam, A. Rountev, and P. Sadayappan. Automatic transformations for communication-minimized parallelization and locality optimization in the polyhedral model. In *International Conference on Compiler Construction*, Apr. 2008.

M. Baskaran, Uday Bondhugula, S. Krishnamoorthy, J. Ramanujam, A. Rountev, and P. Sadayappan. A Compiler Framework for Optimization of Affine Loop Nests

for GPGPUs. In ACM International Conference on Supercomputing (ICS), June 2008.

M. Baskaran, Uday Bondhugula, S. Krishnamoorthy, J. Ramanujam, A. Rountev, and P. Sadayappan. Automatic Data Movement and Computation Mapping for Multilevel Parallel Architectures with Explicitly Managed Memories. In *ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming*, Feb 2008.

Uday Bondhugula, J. Ramanujam, and P. Sadayappan. Automatic mapping of nested loops to FPGAs. In *ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming*, Mar 2007.

S. Krishnamoorthy, M. Baskaran, Uday Bondhugula, J. Ramanujam, A. Rountev, and P. Sadayappan. Effective automatic parallelization of stencil computations. In *ACM SIGPLAN Conference on Programming Language Design and Implementation*, Jun 2007.

Uday Bondhugula, A. Devulapalli, J. Dinan, J. Fernando, P. Wyckoff, E. Stahlberg, and P. Sadayappan. Hardware/software integration for FPGA-based all-pairs shortest-paths. In *IEEE Field Programmable Custom Computing Machines*, Apr 2006.

Uday Bondhugula, A. Devulapalli, J. Fernando, P. Wyckoff, and P. Sadayappan. Parallel FPGA-based all-pairs shortest-paths in a directed graph. In *IEEE International Parallel and Distributed Processing Symposium*, Apr 2006.

S. Sur, Uday Bondhugula, A. Mamidala, H.-W. Jin, and D. K. Panda. High performance RDMA-based all-to-all broadcast for InfiniBand clusters. In 12<sup>th</sup> IEEE International Conference on High Performance Computing, Dec 2005.

## FIELDS OF STUDY

Major Field: Computer Science and Engineering

Emphasis: Automatic parallelization, Parallelizing compilers, Polyhedral model

# TABLE OF CONTENTS

|      |        |                                         | Pa | age   |

|------|--------|-----------------------------------------|----|-------|

| Abst | ract . |                                         |    | ii    |

| Ackn | owle   | dgments                                 |    | iv    |

| Vita |        |                                         |    | vi    |

| List | of Fig | gures                                   |    | xii   |

| List | of Ta  | bles                                    |    | xvii  |

| List | of Alg | gorithms                                |    | xviii |

| Chap | oters: |                                         |    |       |

| 1.   | Int    | $\operatorname{roduction}$              | •  | 1     |

| 2.   | Bac    | ckground                                | •  | 9     |

|      | 2.1    | Hyperplanes and Polyhedra               |    | 10    |

|      | 2.2    | The Polyhedral Model                    |    | 14    |

|      | 2.3    | Polyhedral Dependences                  |    | 17    |

|      |        | 2.3.1 Dependence polyhedron             |    | 18    |

|      |        | 2.3.2 Strengths of dependence polyhedra |    | 19    |

|      | 2.4    | Polyhedral Transformations              |    | 21    |

|      |        | 2.4.1 Why affine transformations?       |    | 25    |

|      | 2.5    | Putting the Notation Together           |    | 27    |

|      | 2.6    | Legality and Parallelism                |    | 28    |

| 3. | Aut                    | tomatic transformations                              | 32 |

|----|------------------------|------------------------------------------------------|----|

|    | 3.1                    | Schedules, Allocations, and Partitions               | 32 |

|    | 3.2                    | Limitations of Previous Techniques                   | 33 |

|    |                        | 3.2.1 Scheduling + allocation approaches             | 33 |

|    |                        | 3.2.2 Existing partitioning-based approaches         | 36 |

|    | 3.3                    | Recalling the Notation                               | 38 |

|    | 3.4                    | Problem Statement                                    | 40 |

|    | 3.5                    | Legality of Tiling in the Polyhedral Model           | 40 |

|    | 3.6                    | Towards Finding Good Solutions                       | 44 |

|    | 3.7                    | Cost Function                                        | 47 |

|    | 3.8                    | Cost Function Bounding and Minimization              | 48 |

|    | 3.9                    | Iteratively Finding Independent Solutions            | 51 |

|    |                        | Communication and Locality Optimization Unified      | 53 |

|    |                        | 3.10.1 Space and time in transformed iteration space | 54 |

|    | 3.11                   | Examples                                             | 55 |

|    |                        | 3.11.1 A step by step example                        | 55 |

|    |                        | 3.11.2 Example 2: Imperfectly nested 1-d Jacobi      | 61 |

|    | 3.12                   | Handling Input Dependences                           | 62 |

|    |                        | Refinements for Cost Function                        | 62 |

|    |                        | Loop Fusion                                          | 63 |

|    |                        | Summary                                              | 64 |

|    |                        | Comparison with Existing Approaches                  | 66 |

|    |                        | Scope for Extensions                                 | 71 |

|    |                        | 1                                                    |    |

| 4. | $\mathbf{Int}\epsilon$ | egrating Loop Fusion: Natural Task                   | 73 |

|    | 4.1                    | Automatic Fusion                                     | 75 |

|    |                        | 4.1.1 Implications of minimizing $\delta$ for fusion | 76 |

|    |                        | 4.1.2 Dependence cutting schemes                     | 79 |

|    | 4.2                    | Correctness and Completeness                         | 80 |

|    |                        | 4.2.1 Bound on iterative search in Algorithm 2       | 83 |

|    | 4.3                    | Theoretical Complexity of Computing Transformations  | 84 |

|    | 4.4                    | Examples                                             | 85 |

|    |                        | 4.4.1 Sequence of matrix-matrix multiplies           | 85 |

|    |                        | 4.4.2 Multiple statement stencils                    | 86 |

|    |                        | 4.4.3 CCSD (T)                                       | 88 |

|    |                        | 4.4.4. TCF four index transform                      | 20 |

|    |                             | 4.4.5 GEMVER                                              | 90  |

|----|-----------------------------|-----------------------------------------------------------|-----|

|    | 4.5                         | Past Work on Fusion                                       | 90  |

| 5. | $\operatorname{Th}\epsilon$ | e PLUTO Parallelization System                            | 97  |

|    | 5.1                         | Overview of PLUTO                                         | 97  |

|    | 5.2                         | Tiled Code Generation under Transformations               | 100 |

|    |                             | 5.2.1 Syntactic tiling versus tiling scattering functions | 101 |

|    |                             | 5.2.2 Tiles under a transformation                        | 102 |

|    |                             | 5.2.3 Pipelined parallel code generation                  | 108 |

|    |                             | 5.2.4 Example 1: Imperfectly nested stencil               | 111 |

|    |                             | 5.2.5 Example 2: LU                                       | 112 |

|    | 5.3                         | Preventing Code Expansion in Tile Space                   | 114 |

|    | 5.4                         | Tilability Detection and Parallelism Detection            | 115 |

|    |                             | 5.4.1 AST-based versus scattering function-based          | 115 |

|    |                             | 5.4.2 Intricacies in detecting tilable bands              | 116 |

|    | 5.5                         | Setting Tile Sizes                                        | 121 |

|    | 5.6                         | Post-processing Transformations                           | 122 |

|    |                             | 5.6.1 Unroll-jamming or register tiling                   | 123 |

|    |                             | 5.6.2 Intra-tile reordering and aiding auto-vectorization | 124 |

|    | 5.7                         | Related Work on Tiled Code Generation                     | 125 |

| 6. | Exp                         | perimental Evaluation                                     | 127 |

|    | 6.1                         | Comparing with previous approaches                        | 127 |

|    | 6.2                         | Experimental Setup                                        | 129 |

|    | 6.3                         | Imperfectly Nested Stencils                               | 130 |

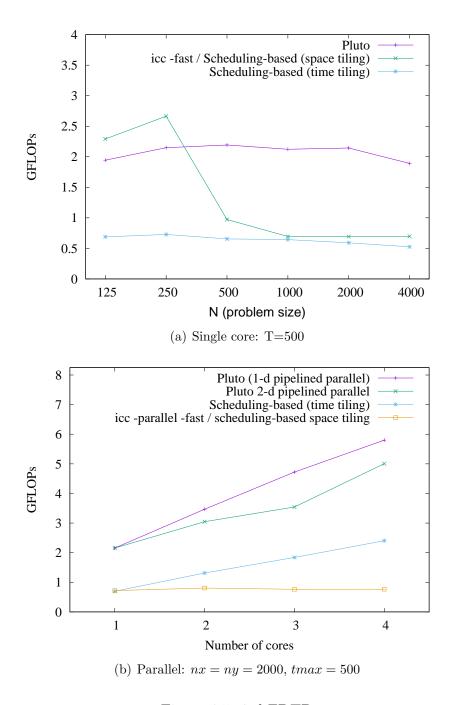

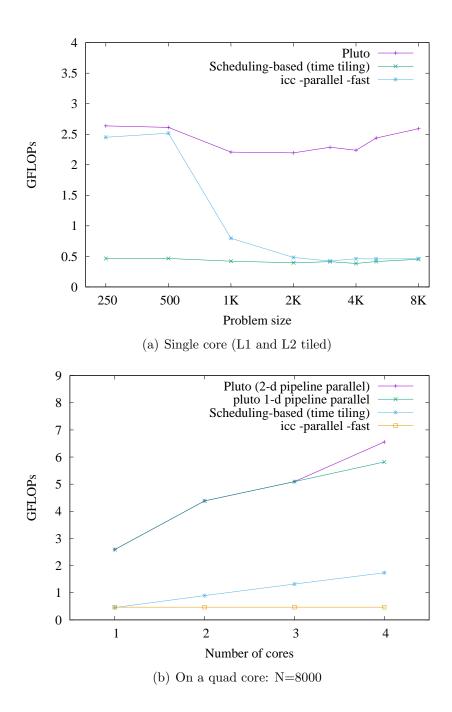

|    | 6.4                         | Finite Difference Time Domain                             | 133 |

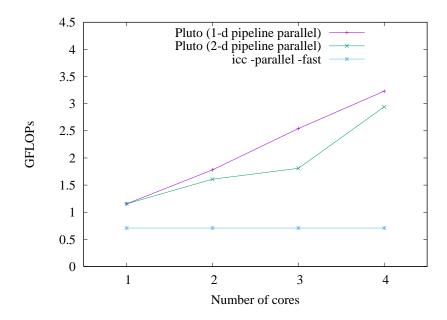

|    | 6.5                         | LU Decomposition                                          | 137 |

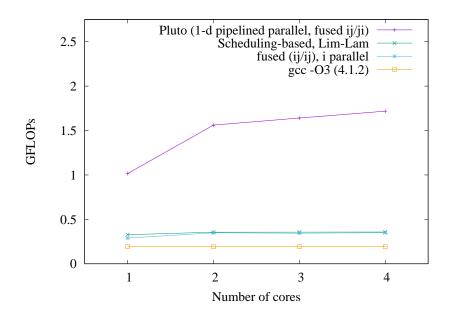

|    | 6.6                         | Matrix Vector Transpose                                   | 141 |

|    | 6.7                         | 3-D Gauss-Seidel successive over-relaxation               | 143 |

|    | 6.8                         | DGEMM                                                     | 145 |

|    | 6.9                         | Experiments with Fusion-critical Codes                    | 145 |

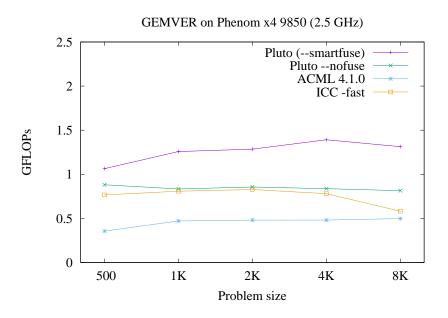

|    |                             | 6.9.1 GEMVER                                              | 147 |

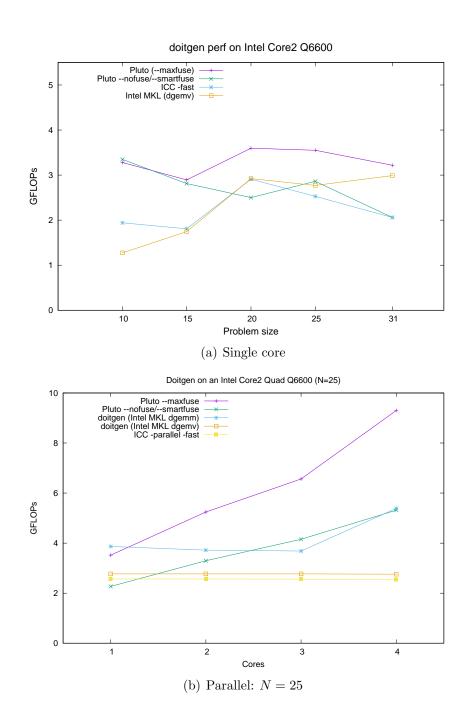

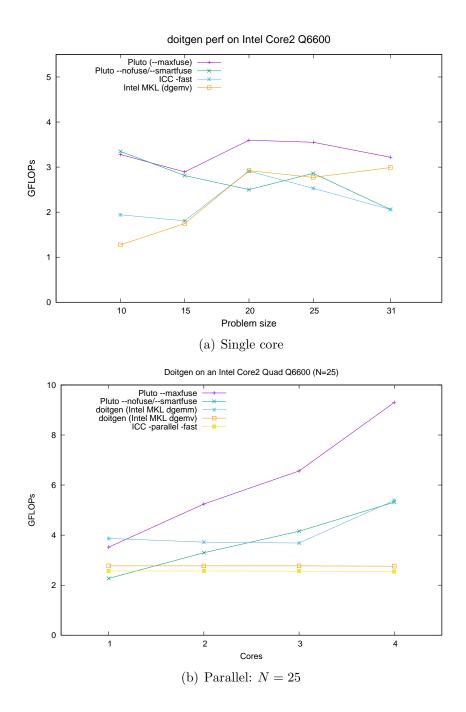

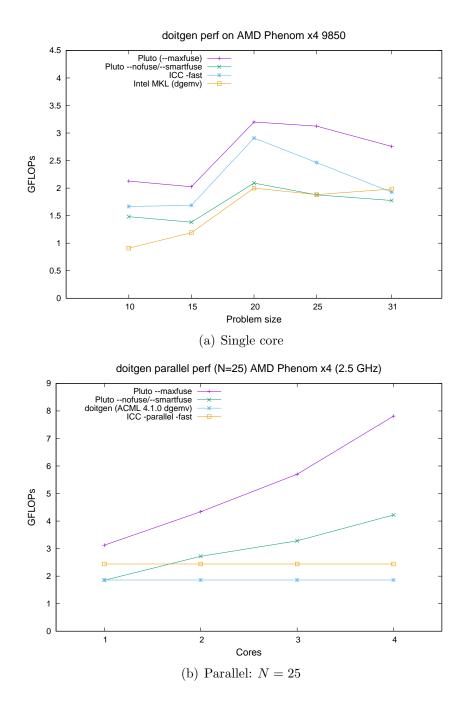

|    |                             | 6.9.2 Doitgen                                             | 150 |

|    | 6.10                        | Analysis                                                  | 150 |

| 7.     | Conclusions and Future Directions     | 156 |

|--------|---------------------------------------|-----|

| Biblio | ography                               | 162 |

| Index  | · · · · · · · · · · · · · · · · · · · | 173 |

# LIST OF FIGURES

| Figu | ire                                                                                                                  | Page |

|------|----------------------------------------------------------------------------------------------------------------------|------|

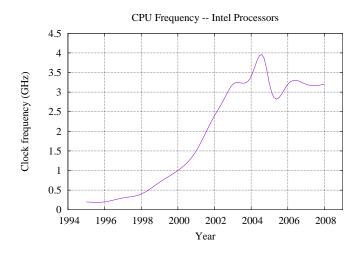

| 1.1  | Clock frequency of Intel processors in the past decade                                                               | 2    |

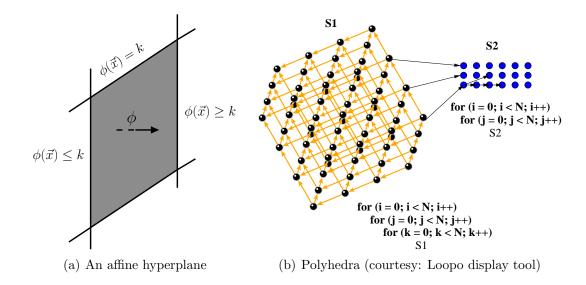

| 2.1  | Hyperplane and Polyhedron                                                                                            | 12   |

| 2.2  | A portion of the GEMVER kernel                                                                                       | 16   |

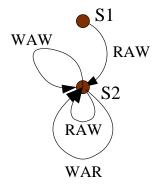

| 2.3  | The data dependence graph                                                                                            | 16   |

| 2.4  | Domain for statement S1 from Figure 2.2                                                                              | 16   |

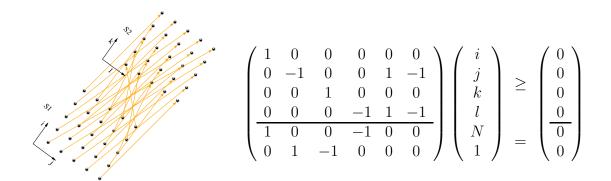

| 2.5  | Flow dependence from $A[i][j]$ of S1 to $A[l][k]$ of S2 and its dependence polyhedron (courtesy: Loopo display tool) | 18   |

| 2.6  | An imperfect loop nest                                                                                               | 20   |

| 2.7  | Dependence polyhedron: $S4(hz[i][j]) \rightarrow S2(hz[i-1][j]) \dots \dots$                                         | 20   |

| 2.8  | Polyhedral transformation: an example                                                                                | 23   |

| 2.9  | Outer parallel loop, $i$ : hyperplane $(1,0)$                                                                        | 29   |

| 2.10 | Inner parallel loop, $j$ : hyperplane $(0,1)$                                                                        | 29   |

| 2.11 | Pipelined parallel loop: $i$ or $j$                                                                                  | 30   |

| 3.1  | A typical solution with scheduling-allocation                                                                        | 36   |

| 3.2  | A fine-grained affine schedule                                                                                       | 36   |

| 3.3  | Affine partitioning with no cost function can lead to unsatisfactory solutions                                       | 37   |

| 3.4  | A good set of $\phi$ s: $(1,0)$ and $(1,1)$                                                                       | 38 |

|------|-------------------------------------------------------------------------------------------------------------------|----|

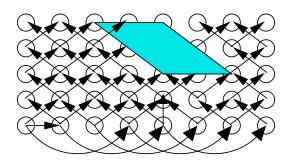

| 3.5  | Tiling an iteration space                                                                                         | 41 |

| 3.6  | No 2-d tiling possible                                                                                            | 42 |

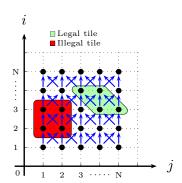

| 3.7  | A legal and an illegal tile                                                                                       | 42 |

| 3.8  | 1-d Jacobi: perfectly nested                                                                                      | 44 |

| 3.9  | 1-d Jacobi: imperfectly nested                                                                                    | 44 |

| 3.10 | Communication volume with different valid hyperplanes for 1-d Jacobi: shaded tiles are to be executed in parallel | 45 |

| 3.11 | Example: Non-uniform dependences                                                                                  | 56 |

| 3.12 | Imperfectly nested Jacobi stencil parallelization: $N=10^6,T=10^5$ .                                              | 61 |

| 4.1  | Fusion: simple example                                                                                            | 77 |

| 4.2  | Lexicographic $\mathbf{u}.\vec{n} + w$ reduction for fusion                                                       | 77 |

| 4.3  | No fusion possible                                                                                                | 78 |

| 4.4  | Two matrix vector multiplies                                                                                      | 78 |

| 4.5  | Sequence of MMs                                                                                                   | 86 |

| 4.6  | Stencils involving multiple statements                                                                            | 87 |

| 4.7  | CCSD (T) code                                                                                                     | 88 |

| 4.8  | CCSD (T): Pluto transformed code: maximally fused. X and Y have been reduced to scalars from 6-dimensional arrays | 89 |

| 4.9  | TCE 4-index transform (original specification)                                                                    | 91 |

| 4.10 | Transformed TCE code (thing and parallelization is not shown): 11, T3 can be contracted to scalars, while T2 and B to a 2-d array and a 3-d array respectively | 92  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.11 | The GEMVER kernel                                                                                                                                              | 92  |

| 4.12 | GEMVER nested loop code                                                                                                                                        | 93  |

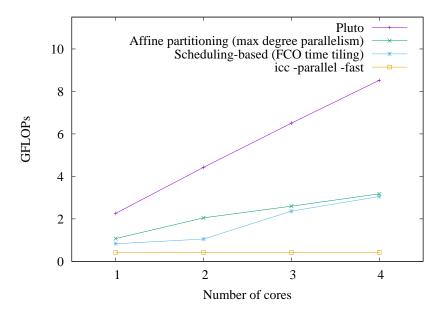

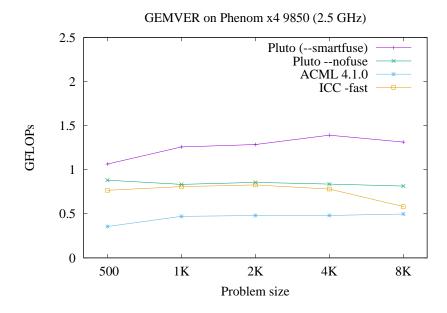

| 4.13 | GEMVER performance: preview (detailed results in Chapter 6)                                                                                                    | 93  |

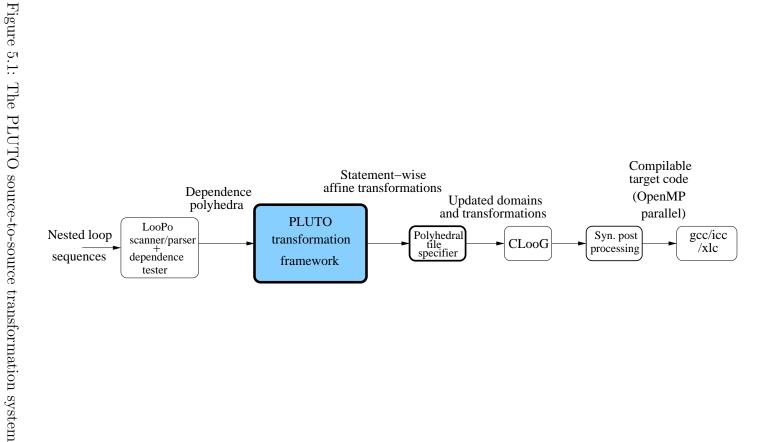

| 5.1  | The PLUTO source-to-source transformation system                                                                                                               | 98  |

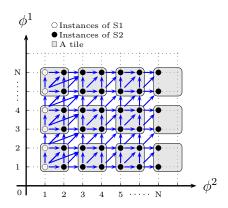

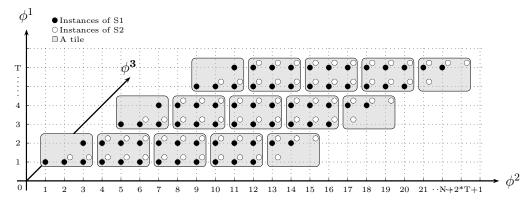

| 5.2  | Imperfectly nested Jacobi stencil: tiling                                                                                                                      | 106 |

| 5.3  | Imperfectly nested Jacobi: tiled code (context: $N \geq 4$ )                                                                                                   | 107 |

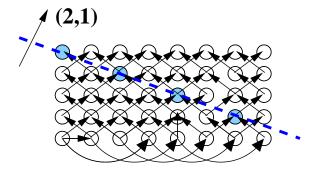

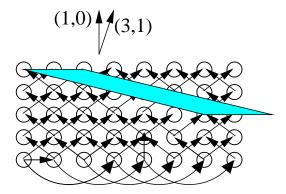

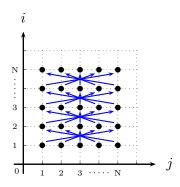

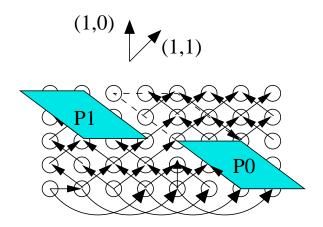

| 5.4  | Tile wavefront along $(2,1)$                                                                                                                                   | 109 |

| 5.5  | Original (sequential) code                                                                                                                                     | 110 |

| 5.6  | Shared memory parallel code generation example: a coarse-grained tile schedule                                                                                 | 110 |

| 5.7  | LU decomposition (non-pivoting) form                                                                                                                           | 111 |

| 5.8  | Doitgen (original code)                                                                                                                                        | 117 |

| 5.9  | Doitgen tiled code (register tiling and vector pragmas not shown) $$ . $$                                                                                      | 119 |

| 5.10 | Doitgen performance on an Intel Core 2 Quad: preview                                                                                                           | 120 |

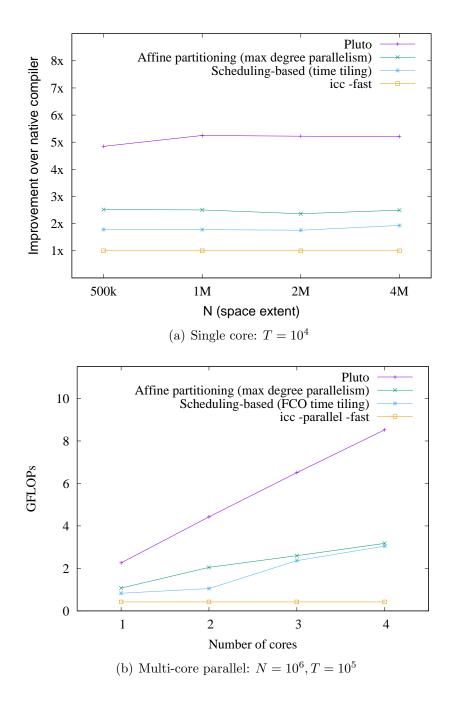

| 6.1  | Imperfectly nested 1-d Jacobi stencil: all codes compiled with ICC                                                                                             | 131 |

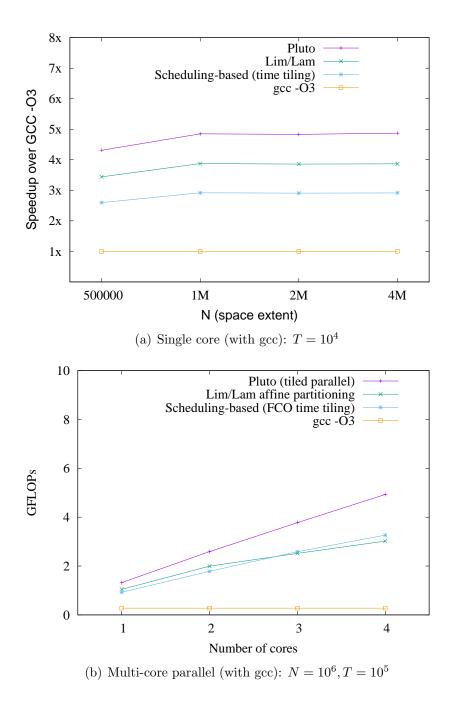

| 6.2  | Imperfectly nested 1-d Jacobi stencil: all codes compiled with GCC $$ .                                                                                        | 132 |

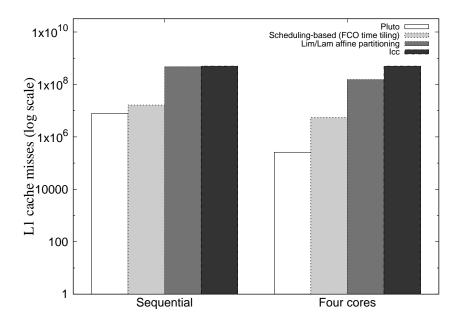

| 6.3  | 1-d Jacobi: L1 tiling: $N = 10^5, T = 10^4$ (note the log scale on y-axis)                                                                                     | 134 |

| 6.4  | 2-d Finite Difference Time Domain: original code and the statement-wise transformation                             | 135 |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

| 6.5  | 2-d FDTD                                                                                                           | 136 |

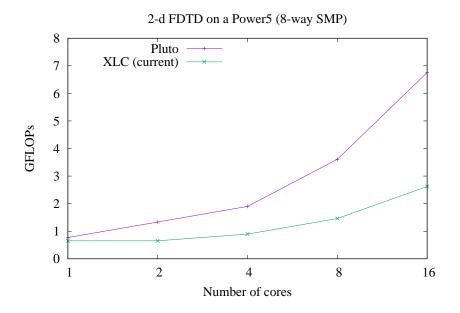

| 6.6  | 2-D FDTD on an 8-way Power5 SMP                                                                                    | 137 |

| 6.7  | LU decomposition (non-pivoting) form                                                                               | 138 |

| 6.8  | LU decomposition parallelized code (register tiling, L2 tiling, and vector pragmas not shown); context: $N \geq 2$ | 139 |

| 6.9  | LU performance                                                                                                     | 140 |

| 6.10 | Matrix vector transpose                                                                                            | 141 |

| 6.11 | MVT performance on a quad core: N=8000 $\dots$                                                                     | 142 |

| 6.12 | 3-d Seidel code (original) and transformation                                                                      | 143 |

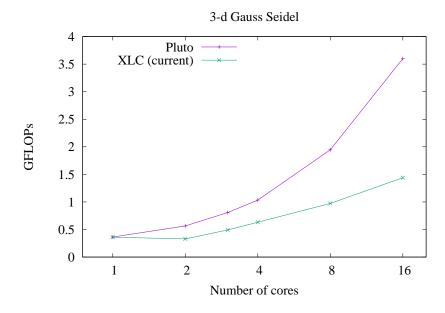

| 6.13 | 3-D Gauss Seidel on Intel Q6600: $N_x=N_y=2000; T=1000$                                                            | 144 |

| 6.14 | 3-D Gauss Seidel on an 8-way Power<br>5 SMP: $N_x=N_y=2000;T=1000$                                                 | 144 |

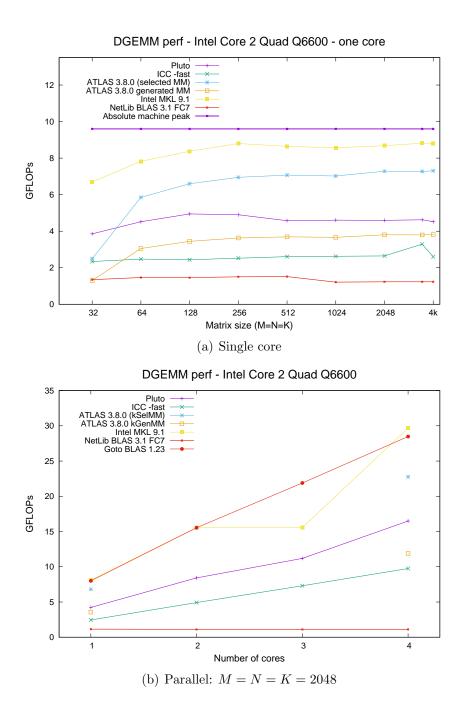

| 6.15 | DGEMM perf: Pluto vs. Hand-tuned                                                                                   | 146 |

| 6.16 | GEMVER (high-level specification)                                                                                  | 147 |

| 6.17 | Nested loops for GEMVER                                                                                            | 148 |

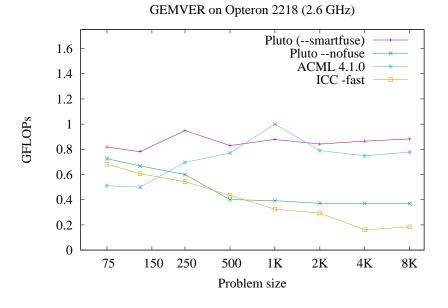

| 6.18 | GEMVER on Opteron                                                                                                  | 148 |

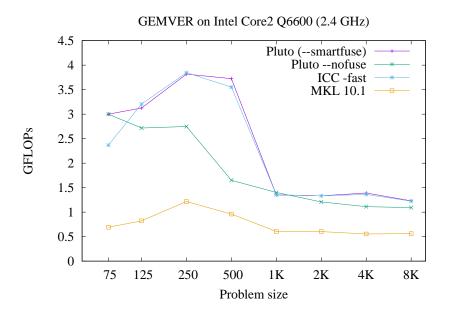

| 6.19 | GEMVER on Intel Core 2 Quad                                                                                        | 149 |

| 6.20 | GEMVER on AMD Phenom x4 9850                                                                                       | 149 |

| 6 21 | Doitgen                                                                                                            | 151 |

| 6.22 | Doitgen | tiled | code | (register | tiling | and | vector | pragm | ıas | not | sho | wn <sub>.</sub> | ) | <br>152 |

|------|---------|-------|------|-----------|--------|-----|--------|-------|-----|-----|-----|-----------------|---|---------|

| 6.23 | Doitgen | on an | Inte | l Core 2  | Quad   |     |        |       |     |     |     |                 |   | <br>153 |

| 6.24 | Doitgen | on A  | MD F | henom x   | κ4     |     |        |       |     |     |     |                 |   | <br>154 |

# LIST OF TABLES

| Tab | le I                                                                                                                                       | Page |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.1 | Time to compute transformations as of Pluto version 0.3.1 on an Intel Core2 Quad Q6600                                                     | 85   |

| 5.1 | Performance sensitivity of L1-tiled imperfectly nested stencil code with Cloog options: $N=10^6,T=1000,$ tile dimensions: $2048\times2048$ | 114  |

# LIST OF ALGORITHMS

| 1 | Pluto automatic transformation algorithm             | 64  |

|---|------------------------------------------------------|-----|

| 2 | Pluto algorithm (with fusion heuristics)             | 81  |

| 3 | Tiling for multiple statements under transformations | 103 |

| 4 | Code generation for tiled pipelined parallelism      | 108 |

#### CHAPTER 1

## INTRODUCTION

Current trends in microarchitecture are towards larger number of processing elements on a single chip. Till the early 2000s, increasing the clock frequency of microprocessors gave most software a performance boost without any additional effort on part of the programmers, or much effort on part of compiler or language designers. However, due to power dissipation issues, it is now no longer possible to increase clock frequencies the same way it had been (Figure 1.1). Increasing the number of cores on the chip has currently become the way to use the ever increasing number of transistors available, while keeping power dissipation in control. Multi-core processors appear in all realms of computing – high performance supercomputers built out of commodity processors, accelerators like the Cell processor and general-purpose GPUs and multi-core desktops. Besides mainstream and high-end computing, the realm of embedding computing cannot be overlooked. Multiprocessor System-on-Chip (MP-SoCs) are ubiquitous in the embedding computing domain for multimedia and image processing.

Figure 1.1: Clock frequency of Intel processors in the past decade

End of the ILP era. Dynamic out-of-order execution, superscalar processing, multiple way instruction issuing, hardware dynamic branch prediction and speculative execution, non-blocking caches, were all techniques to increase instruction-level parallelism (ILP), and thus improve performance for "free", i.e., transparent to programmers and without much assistance from compilers or programming languages. Compilers were taken for "granted" and programmers would mainly expect correct code generated for them. In general, compiler optimizations have had a narrow audience [Rob01]. Most of the credit for improved performance would go to the architecture, or to the language designer for higher productivity. However, currently, efforts to obtain more ILP have reached a dead-end with no more ILP left to be extracted. This is mainly because ILP works well within a window of instructions of bounded length. Extracting a much more coarser granularity of parallelism, thread-level par-

allelism, requires looking across instructions that are possibly thousands or millions of instructions away in the dynamic length of a program. The information that they can be executed in parallel is obviously something that hardware does not have, or is at least not feasible to be done by hardware alone at runtime. Analyses and transformation that can achieve the above can only be performed at a high level – by a software system like the language translator or a compiler.

Computers with multiple processors have a very long history. Special-purpose parallel computers like massively parallel processors (MPPs), systolic arrays, or vector supercomputers were the dominant form of computers or supercomputers up till the early 1990s. However, all of these architectures slowly disappeared with the arrival of single-threaded superscalar microprocessors. These microprocessors continuously delivered ever increasing performance without requiring any advanced parallel compiler technology. As mentioned before, this was due to techniques to obtain more and more ILP and increasing clock speed keeping up with Moore's law. Even a majority of the supercomputers today are built out of commodity superscalar processors [Top]. Hence, due to the absence of parallelism in the mainstream for the past decade and a half, parallel compiler and programming technology stagnated. However, with parallelism and multi-core processors becoming mainstream, there is renewed interest and urgency in supporting parallel programming at various levels – languages, compilers, libraries, debuggers, and runtime systems. It is clear that hardware architects no longer have a solution by themselves.

Parallelism and Locality. Besides multiple cores on a chip, caches or faster onchip memories and registers have been around for a long time and are likely to stay. Often, not optimizing for locality has a direct impact on parallelization. This is because of the fact that increasing the number of threads increases the amount of memory bandwidth needed for the computation: the amount of available memory bandwidth has always lagged computational power. Hence, optimizing for parallelism and locality are the central issues in improving performance.

Difficulty of parallel programming. The difficulty of programming multi-core architectures to effectively use multiple on-chip processing units is a significant challenge. This is due to several reasons. Writing programs with a single thread of logic is quite intuitive and natural, and so nearly all programmers have been used to writing sequential programs for decades. One can think of two broad approaches of transitioning from sequential programs to parallel ones: (1) proceed incrementally, i.e., get a basic sequential code working and then parallelize it, and (2) design and code a parallel program from the start itself. With the former approach, manually parallelizing an application written to be sequential can be quite tedious. In some cases, the parallelization may be non-trivial enough to be infeasible to be done by hand, or even detect manually. The second approach goes against one of the basic philosophies of programming which says, "pre-mature optimization is the root of all evil". Thinking about parallelism from the very start of the development process may make the path to obtain a correct working version of a program itself difficult. In any case, all of

the manual techniques are often not productive for the programmer due to the need to synchronize access to data shared by threads.

Automatic Parallelization. Among several approaches to address the parallel programming problem, one that is very promising but simultaneously very challenging is automatic parallelization. Automatic parallelization is the process of automatically converting a sequential program to a version that can directly run on multiple processing elements without altering the semantics of the program. This process requires no effort on part of the programmer in parallelization and is therefore very attractive. Automatic parallelization is typically performed in a compiler, at a high level where most of the information needed is available. The output of an auto-parallelizer is a race-free deterministic program that obtains the same results as the original sequential program. This dissertation deals with compile-time automatic parallelization and primarily targets shared memory parallel architectures for which auto-parallelization is significantly easier. A common feature of all of the multicore architectures we have named so far is that they all have shared memory at one level or the other.

The Polyhedral Model. Many compute-intensive applications often spend most of their execution time in nested loops. This is particularly common in scientific and engineering applications. The polyhedral model provides a powerful abstraction to reason about transformations on such loop nests by viewing a dynamic instance (iteration) of each statement as an integer point in a well-defined space called the statement's *polyhedron*. With such a representation for each statement and a precise

characterization of inter and intra-statement dependences, it is possible to reason about the correctness of complex loop transformations in a completely mathematical setting relying on machinery from linear algebra and integer linear programming. The transformations finally reflect in the generated code as reordered execution with improved cache locality and/or loops that have been parallelized. The polyhedral model is readily applicable to loop nests in which the data access functions and loop bounds are affine functions (linear function with a constant) of the enclosing loop variables and parameters. While a precise characterization of data dependences is feasible for programs with static control structure and affine references and loop-bounds, codes with non-affine array access functions or code with dynamic control can also be handled, but primarily with conservative assumptions on some dependences.

The task of program optimization (often for parallelism and locality) in the polyhedral model may be viewed in terms of three phases: (1) static dependence analysis of the input program, (2) transformations in the polyhedral abstraction, and (3) generation of code for the transformed program. Significant advances were made in the past decade on dependence analysis [Fea91, Fea88, Pug92] and code generation [AI91, KPR95, GLW98] in the polyhedral model, but the approaches suffered from scalability challenges. Recent advances in dependence analysis and more importantly in code generation [QRW00, Bas04a, VBGC06, VBC06] have solved many of these problems resulting in the polyhedral techniques being applied to code representative of real applications like the spec2000fp benchmarks [CGP+05, GVB+06]. These advances have also made the polyhedral model practical in production compiler con-

texts [PCB<sup>+</sup>06] as a flexible and powerful representation to compose and apply transformations. However, current state-of-the-art polyhedral implementations still apply transformations manually and significant time is spent by an expert to determine the best set of transformations that lead to improved performance [CGP<sup>+</sup>05, GVB<sup>+</sup>06]. Regarding the middle step, an important open issue is that of the choice of transformations from the huge space of valid transforms. Existing automatic transformation frameworks [LL98, LCL99, LLL01, AMP01, Gri04] have one or more drawbacks or restrictions in finding *good* transformations. All of them lack a practical and scalable cost model for effective coarse-grained parallel execution and locality as is used with manually developed parallel applications.

This dissertation describes a new approach to address this problem of automatically finding good transformations to simultaneously optimize for coarse-grained parallelism and locality. Our approach is driven by a powerful and practical linear cost function that goes beyond just maximizing the number of degrees of parallelism or minimizing the order of synchronization. The cost function allows finding good ways to tile and fuse across multiple statements coming from sequences of arbitrarily nested loops. The entire framework has been implemented into a tool, PLUTO, that can automatically generate OpenMP parallel code from regular C program sections. In this process, we also describe techniques to generate efficient tiled and parallel code, along with a number of other optimizations to achieve high performance on modern multicore architectures.

Experimental results from the implemented system show very high speedups for local and parallel execution on multicores over state-of-the-art research compiler frameworks as well as the best native production compilers. For several linear algebra kernels, code generated from Pluto beats, by a significant margin, the same kernels implemented with sequences of calls to hand-tuned BLAS libraries supplied by vendors. The system also leaves a lot of scope for further improvement in performance. Thanks to the mathematical abstraction provided by the polyhedral model, Pluto can also serve as the backend for parallel code generation with new domain-specific frontends.

The rest of this dissertation is organized as follows. Chapter 2 provides the mathematical background for the polyhedral model. Chapter 3 describes our automatic transformation framework. Chapter 4 is devoted to explaining how loop fusion is naturally handled in an integrated manner in our framework. Chapter 5 describes the implemented Pluto system along with details on parallel and tiled code generation and complementary post-processing. Chapter 6 provides an experimental evaluation of the framework. Conclusions and directions for future research are finally presented in Chapter 7. Most of the content in Chapters 3 and 5, and some results from Chapter 6 have been published in [BBK+08c] and [BHRS08].

## CHAPTER 2

### BACKGROUND

In this chapter, we present a overview of the polyhedral model, and introduce notation used throughout the dissertation. The mathematical background on linear algebra and linear programming required to understand the theoretical aspects of this dissertation is fully covered in this chapter. A few fundamental concepts and definitions relating to cones, polyhedra, and linear inequalities have been omitted and they can be found in [Wil93] and [Sch86]. Detailed background on traditional loop transformations can be found in [Wol95, Ban93]. Overall, I expect the reader to find the background presented here self-contained. [Bas04b, Gri04] are among other sources for introduction to the polyhedral model.

All row vectors will be typeset in bold lowercase, while regular vectors are typeset with an overhead arrow. The set of all real numbers, the set of rational numbers, and the set of integers are represented by  $\mathbb{R}$ ,  $\mathbb{Q}$ , and  $\mathbb{Z}$ , respectively.

#### 2.1Hyperplanes and Polyhedra

**Definition 1** (Linear). A k-dimensional function f is linear iff it can expressed in the following form:

linear function

$$f(\vec{v}) = M_f \vec{v}$$

(2.1)

where

$$\vec{v} = \begin{pmatrix} v_1 \\ \vdots \\ v_d \end{pmatrix}$$

and  $M_f \in \mathbb{R}^{k \times d}$  is a matrix with  $k$  rows and  $d$  columns. In our context,  $M_f$  is an integer matrix, i.e.,  $M_f \in \mathbb{Z}^{k \times d}$

**Definition 2** (Affine). A k-dimensional function f is affine iff it can expressed in the following form:

affine function

$$f(\vec{v}) = M_f \vec{v} + \vec{f_0}$$

(2.2)

where

$$\vec{v} = \begin{pmatrix} v_1 \\ \vdots \\ v_d \end{pmatrix}$$

and  $M_f \in \mathbb{R}^{k \times d}$  is a matrix with  $k$  rows and  $d$  columns,  $f_0 \in \mathbb{R}^k$  is a  $k$ -dimensional vector. In all cases, we deal with affine functions with  $M_f \in \mathbb{Z}^{k \times d}$  and  $f_0 \in \mathbb{Z}^k$ . The domain is also a set of integers:  $\vec{v} \in \mathbb{Z}^d$ .

**Definition 3** (Null space). The *null space* of an affine function  $f(\vec{v}) = M_f \vec{v} + \vec{f_0}$  is  $\left\{ \vec{x} \mid f(\vec{x}) = \vec{0} \right\}.$

f is a one-to-one mapping iff  $M_f$  has full column rank, i.e., if it has as many linearly independent rows (and columns) as the number of its columns. In such a case, the null space is 0-dimensional, i.e., trivially the vector 0.

**Definition 4** (Affine spaces). A set of vectors is an affine space iff it is closed under affine combination, i.e., if  $\vec{x}$ ,  $\vec{y}$  are in the space, all points lying on the line joining  $\vec{x}$  and  $\vec{y}$  belong to the space.

A line in a vector space of any dimensionality is a one-dimensional affine space. In 3-d space, any 2-d plane is an example of a 2-d affine sub-space. Note that 'affine function' as defined in (2.2) should not be confused with 'affine combination', though several researchers use the term affine combination in place of an affine function.

**Definition 5** (Affine hyperplane). An affine hyperplane is an n-1 dimensional affine sub-space of an n dimensional space.

In our context, the set of all vectors  $v \in \mathbb{Z}^n$  such that  $\mathbf{h}.\vec{v} = k$ , for  $k \in \mathbb{Z}$ , forms an affine hyperplane. The set of parallel *hyperplane instances* correspond to different values of k with the row vector  $\mathbf{h}$  normal to the hyperplane. Two vectors  $\vec{v_1}$  and  $\vec{v_2}$  lie in the same hyperplane if  $\mathbf{h}.\vec{v_1} = \mathbf{h}.\vec{v_2}$ . An affine hyperplane can also be viewed as a one-dimensional affine function that maps an n-dimensional space onto a one-dimensional space, or partitions an n-dimensional space into n-1 dimensional slices. Hence, as a function, it can be written as:

$$\phi(\vec{v}) = \mathbf{h}.\vec{v} + c \tag{2.3}$$

Figure 2.1(a) shows a hyperplane geometrically. Throughout the dissertation, the hyperplane is often referred to by the row vector,  $\mathbf{h}$ , the vector normal to the hyperplane. A hyperplane  $\mathbf{h}.\vec{v} = k$  divides the space into two half-spaces, the positive half-space,

Figure 2.1: Hyperplane and Polyhedron

$h.\vec{v} \ge k$ , and a negative half-space,  $\mathbf{h}.\vec{v} \le k$ . Each half-space can be represented by an affine inequality.

**Definition 6** (**Polyhedron**, **Polytope**). A *polyhedron* is an intersection of a finite number of half-spaces. A *polytope* is a bounded polyhedron.

Each of the half-spaces provides a face to the polyhedron. Hence, the set of affine inequalities, each representing a face, can be used to compactly represent the polyhedron. If there are m inequalities, then the polyhedron is

$$\left\{ \vec{x} \in \mathbb{R}^n \mid A\vec{x} + \vec{b} \ge \vec{0} \right\}$$

where  $A \in \mathbb{R}^{m \times n}$  and  $\vec{b} \in \mathbb{R}^m$ .

A polyhedron also has an alternate dual representation in terms of vertices, rays, and lines, and algorithms like the Chernikova algorithm [LeV92] exist to move from the face representation to the vertex one. Polylib [Pol] and PPL [BHZ] are two libraries that provide a range of functions to perform various operations on polyhedra and use the dual representation internally.

In our context, we are always interested in the integer points inside a polyhedron since loop iterators typically have integer data types and traverse an integer space. The matrix A and  $\vec{b}$  for problems we will deal with also comprise only integers. So, we always have:

$$\left\{ \vec{x} \in \mathbb{Z}^n \mid A\vec{x} + \vec{b} \ge \vec{0} \right\} \tag{2.4}$$

where  $A \in \mathbb{Z}^{m \times n}$  and  $\vec{b} \in \mathbb{Z}^m$ .

Lemma 1 (Affine form of the Farkas lemma). Let  $\mathcal{D}$  be a non-empty polyhedron defined by p affine inequalities or faces

$$\mathbf{a_k} \cdot \vec{x} + b_k \ge 0, \quad k = 1, p$$

then, an affine form  $\psi$  is non-negative everywhere in  $\mathcal{D}$  iff it is a non-negative linear combination of the faces:

$$\psi(\vec{x}) \equiv \lambda_0 + \sum_{k=1}^p \lambda_k \left( \mathbf{a_k} \vec{x} + b_k \right), \quad \lambda_0, \lambda_1, \dots, \lambda_p \ge 0$$

(2.5)

The non-negative constants  $\lambda_k$  are referred to as the Farkas multipliers. Proof of the *if* part is obvious. For the *only if* part, see Schrijver [Sch86]. We provide the

main idea here roughly. The polyhedron  $\mathcal{D}$  lies in the non-negative half-space of the hyperplane  $\psi(\vec{x})$ . This makes sure that  $\lambda_0$  has to be non-negative if the hyperplane is pushed close enough to the polytope so that it touches a vertex of the polyhedron first without cutting the polyhedron. If a hyperplane passes through a vertex of the polyhedron and with the entire polyhedron in its non-negative half-space, the fact that it can be expressed as a non-negative linear combination of the faces of the polyhedron directly follows from the Fundamental Theorem of Linear Inequalities [Sch86].

**Definition 7** (**Perfect loop nest, Imperfect loop nest**). A set of nested loops is called a *perfect loop nest* iff all statements appearing in the nest appear inside the body of the innermost loop. Otherwise, the loop nest is called an *imperfect loop nest*. Figure 2.6 shows an imperfect loop nest.

**Definition 8** (Affine loop nest). Affine loop nests are sequences of imperfectly nested loops with loop bounds and array accesses that are affine functions of outer loop variables and program parameters.

Program parameters or structure parameters are symbolic constants that appear in loop bounds or access functions. They very often represent the problem size. N is a program parameter in Figure 2.1(b), while in Figure 2.2, N and  $\beta$  are the program parameters.

## 2.2 The Polyhedral Model

The polyhedral model is a geometrical as well as a linear algebraic framework for capturing the execution of a program in a compact form for analysis and transformation. The compact representation is primarily of the dynamic instances of statements of a program surrounded by loops in a program, the dependences between such statements, and transformations.

**Definition 9** (**Iteration vector**). The *iteration vector* of a statement is the vector consisting of values of the indices of all loops surrounding the statement.

Let S be a statement of a program. The iteration vector is denoted by  $\vec{i}_S$ . An iteration vector represents a dynamic instance of a statement appearing in a loop nest that may be nested perfectly or imperfectly.

**Definition 10 (Domain, Index set).** The set of all iteration vectors for a given statement is the *domain* or the *index set* of the statement.

A program comprises a sequence of statements, each statement surrounded by loops in a given order. We denote the domain of a statement S by  $\mathcal{D}^S$ . When the loop bounds and data accesses are affine functions of outer loop indices and other program parameters, and all conditionals are statically predictable, the domain of every statement is a polyhedron as defined in (2.4). Again, conditionals that are affine functions of outer loop indices and program parameters are statically predictable. Affine loop nests with static control are also called static control programs or regular programs. These programs are readily accepted in the polyhedral model. Several of the restrictions for the polyhedral model can be overcome with tricks or conservative assumptions while still making all analysis and transformation meaningful. However, many pose a challenging problem requiring extensions to the model. Techniques

developed and implemented in this thesis apply to all programs for which a polyhedral representation can be extracted. All codes used for experimental evaluation are regular programs with static control.

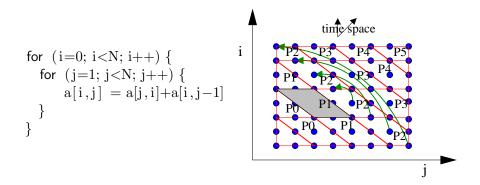

$$\begin{array}{l} \text{for } (i\!=\!0;\, i\!<\!N;\, i\!+\!+) \\ \text{for } (j\!=\!0;\, j\!<\!N;\, j\!+\!+) \\ \text{S1: } A[i,j] = A[i,j]\!+\!u1[i]\!*\!v1[j] \,+\, u2[i]\!*\!v2[j]; \\ \\ \text{for } (k\!=\!0;\, k\!<\!N;\, k\!+\!+) \\ \text{for } (l\!=\!0;\, l\!<\!N;\, l\!+\!+) \\ \text{S2: } x[k] = x[k]\!+\!beta\!*\!A[l,k]\!*\!y[l]; \end{array}$$

Figure 2.2: A portion of the GEMVER kernel

Figure 2.3: The data dependence graph

Each dynamic instance of a statement S, in a program, is identified by its iteration vector  $\vec{i}_S$  which contains values for the indices of the loops surrounding S, from outermost to innermost. A statement S is associated with a polytope  $\mathcal{D}^S$  of dimensionality  $m_S$ . Each point in the polytope is an  $m_S$ -dimensional iteration vector, and

Figure 2.4: Domain for statement S1 from Figure 2.2

the polytope is characterized by a set of bounding hyperplanes. This is true when the loop bounds are linear combinations (with a constant) of outer loop indices and program parameters (typically, symbolic constants representing the problem size).

## 2.3 Polyhedral Dependences

Dependences. Two iterations are said to be dependent if they access the same memory location and one of them is a write. A true dependence exists if the source iteration's access is a write and the target's is a read. These dependences are also called read-after-write or RAW dependences, or flow dependences. Similarly, if a write precedes a read to the same location, the dependence is called a WAR dependence or an anti-dependence. WAW dependences are also called output dependences. Read-after-read or RAR dependences are not actually dependences, but they still could be important in characterizing reuse. RAR dependences are also called input dependences.

Dependences are an important concept while studying execution reordering since a reordering will only be legal if does not violate the dependences, i.e., one is allowed to change the order in which operations are performed as long as the transformed program has the same execution order with respect to the dependent iterations.

**Data Dependence Graph.** The Data Dependence Graph (DDG) G = (V, E) is a directed multi-graph with each vertex representing a statement, i.e.,  $V = \mathbf{S}$ . An edge,  $e \in E$ , from node  $S_i$  to  $S_j$  represents a dependence with the source and target

Figure 2.5: Flow dependence from A[i][j] of S1 to A[l][k] of S2 and its dependence polyhedron (courtesy: Loopo display tool)

conflicting accesses in  $S_i$  and  $S_j$  respectively. Figure 2.3 shows the DDG for the code in Figure 2.2.

## 2.3.1 Dependence polyhedron.

For an edge e, the relation between the dynamic instances of  $S_i$  and  $S_j$  that are dependent is captured by the dependence polyhedron,  $\mathcal{P}_e$ . The dependence polyhedron is in the sum of the dimensionalities of the source and target statement's polyhedra along with dimensions for program parameters. If  $\vec{s}$  and  $\vec{t}$  are the source and target iterations that are dependent, we can express:

$$\langle \vec{s}, \vec{t} \rangle \in \mathcal{P}_e \quad \iff \quad \vec{s} \in \mathcal{D}^{S_i}, \vec{t} \in \mathcal{D}^{S_j} \text{ are dependent through edge } e \in E$$

(2.6)

The ability to capture the exact conditions on when a dependence exists through linear equalities and inequalities rests on the fact that there exists a affine relation between the iterations and the accessed data for regular programs. Equalities can be replaced by two inequalities (' $\geq 0$ ' and ' $\leq 0$ ') and everything can be converted to inequalities in the  $\geq 0$  form, i.e., the polyhedron can be expressed as the intersection of a finite number of non-negative half-spaces. Let the  $i^{th}$  inequality after conversion to such a form be denoted by  $\mathcal{P}_e^i$ . For the code shown in Figure 2.2, consider the dependence between the write at A[i][j] from S1 and the read A[l][k] in S2. The dependence polyhedron for this edge is shown in Figure 2.5.

In the next chapter, we see that the dependence polyhedra is the most important structure around which the problem of finding legal and good transformations centers. In particular, the Farkas lemma (Sec. 2.1) is applied for the dependence polyhedron. A minor point to note here is that the dependence polyhedra we see are often integral polyhedra, i.e., polyhedra that have integer vertices. Hence, the application of Farkas lemma for it is exact and not conservative. Even when the dependence polyhedron is not integral, i.e., when its integer hull is a proper subset of the polyhedron, the difference between applying it to the integer hull and the entire polyhedron is highly unlikely to matter in practice. If need be, one can construct the integer hull of the polyhedron and apply the Farkas lemma on it.

## 2.3.2 Strengths of dependence polyhedra

The dependence polyhedra are a very general and accurate representation of instance-wise dependences which subsume several traditional notions like distance vectors (also called uniform dependences), dependence levels, and direction vectors. Though a similar notion of exact dependences was presented by Feautrier [Fea91] for value-based array dataflow analysis, this notion of dependence polyhedra has only

been sharpened in the past few years by researchers [CGP+05, VBGC06, PBCV07] and is not restricted to programs in single assignment form nor does it require conversion to single-assignment form. Dependence abstractions like direction vectors or distance vectors are tied to a particular syntactic nesting unlike dependence polyhedra which is more abstract and captures the relation between integer points of polyhedra. One could obtain weaker dependence representations from a dependence polyhedra.

```

for (t=0; t< tmax; t++) {

0 < t < T - 1

for (j=0; j< ny; j++)

0 < t' < T - 1

ey[0][j] = t;

0 \le i \le N-1

for (i=1; i< nx; i++)

for (j=0; j< ny; j++)

0 \le j \le N-1

ey[i][j] = ey[i][j] - 0.5*(hz[i][j]-hz[i-1][j]);

0 \le i' \le N - 1

for (i=0; i< nx; i++)

0 < j' < N-1

for (j=1; j< ny; j++)

ex[i][j] = ex[i][j] - 0.5*(hz[i][j]-hz[i][j-1]);

t = t' - 1

for (i=0; i< nx; i++)

i = i' - 1

for (j=0; j< ny; j++)

j = j'

hz[i][j]=hz[i[j] -

0.7*(ex[i][j+1]-ex[i][j]+ey[i+1][j]-ey[i][j]);

}

Figure 2.7:

Dependence

polyhedron: S4(hz[i][j]) \rightarrow

Figure 2.6: An imperfect loop nest

S2(hz[i-1][j])

```

Another example. For the code shown in Figure 2.6, consider the flow dependence between S4 and S2 from the write at hz[i][j] to the read at hz[i-1][j] (later time steps). Let  $\vec{s} \in \mathcal{D}^{S4}$ ,  $\vec{t} \in \mathcal{D}^{S2}$ ,  $\vec{s} = (t, i, j)$ ,  $\vec{t} = (t', i', j')$ ; then,  $\mathcal{P}_e$  for this edge is shown in Figure 2.7.

Uniform and Non-uniform dependences. Uniform dependences traditionally make sense for a statement in perfectly nested loop nest or two statements which are in the same perfectly nested loop body. In such cases a uniform dependence is a dependence where the source and target iteration in question are a constant vector distance apart. Such a dependence is also called a constant dependence and represented as a distance vector [Wol95].

For detailed information on polyhedral dependence analysis and a good survey of older techniques in the literature including non-polyhedral ones, the reader can refer to [VBGC06].

#### 2.4 Polyhedral Transformations

A one-dimensional affine transform for statement S is an affine function defined by:

$$\phi_{S}(\vec{i}) = (c_{1}^{S} c_{2}^{S} \dots c_{m_{S}}^{S}) (\vec{i}_{S}) + c_{0}^{S}$$

$$= (c_{1}^{S} c_{2}^{S} \dots c_{m_{S}}^{S} c_{0}^{S}) (\vec{i}_{S})$$

(2.7)

where  $c_0, c_1, c_2, \ldots, c_{m_S} \in \mathbb{Z}$ ,  $\vec{i} \in \mathbb{Z}^{m_S}$  Hence, a one-dimensional affine transform for each statement can be interpreted as a partitioning hyperplane with normal  $(c_1, \ldots, c_{m_S})$ . A multi-dimensional affine transformation can be represented as a sequence of such  $\phi$ 's for each statement. We use a superscript to denote the hyperplane for each level.  $\phi_S^k$  represents the hyperplane at level k for statement S. If  $1 \le k \le d$ , all the  $\phi_S^k$  can be represented by a single d-dimensional affine function  $\mathcal{T}_S$  given by:

$$\mathcal{T}_S \vec{i}_S = M_S \vec{i}_S + \vec{t}_S \tag{2.8}$$

where  $M_S \in \mathbb{Z}^{d \times m_S}$ ,  $\vec{t}_S \in \mathbb{Z}^d$ .

$$\mathcal{T}_{S}(\vec{i}) = \begin{pmatrix} \phi_{S}^{1}(\vec{i}) \\ \phi_{S}^{2}(\vec{i}) \\ \vdots \\ \phi_{S}^{d}(\vec{i}) \end{pmatrix} = \begin{pmatrix} c_{11}^{S} & c_{12}^{S} & \dots & c_{1m_{S}}^{S} \\ c_{21}^{S} & c_{22}^{S} & \dots & c_{2m_{S}}^{S} \\ \vdots & \vdots & \vdots & \vdots \\ c_{d1}^{S} & c_{d2}^{S} & \dots & c_{dm_{S}}^{S} \end{pmatrix} \vec{i}_{S} + \begin{pmatrix} c_{10}^{S} \\ c_{20}^{S} \\ \vdots \\ c_{d0}^{S} \end{pmatrix}$$

(2.9)

Scalar dimensions. The dimensionality of  $\mathcal{T}_S$ , d, may be greater than  $m_S$  as some rows in  $\mathcal{T}_S$  serve the purpose of representing partially fused or unfused dimensions at a level. Such a row has  $(c_1, \ldots, c_{m_S}) = \mathbf{0}$ , and a particular constant for  $c_0$ . All statements with the same  $c_0$  value are fused at that level and the unfused sets are placed in the increasing order of their  $c_0$ s. We call such a level a scalar dimension. Hence, a level is a scalar dimension if the  $\phi$ 's for all statements at that level are constant functions. Figure 2.8 shows a sequence of matrix-matrix multiplies and how a transformation captures a legal fusion: the transformation fuses ji of S1 with jk of S2;  $\phi^3$  is a scalar dimension.

Complete scanning order. The number of rows in  $M_S$  for each statements should be the same (d) to map all iterations to a global space of dimensionality d. To provide a complete scanning order for each statement, the number of linearly independent  $\phi_S$ 's for a statement should be the same as the dimensionality of the statement,  $m_S$ , i.e.,  $\mathcal{T}_S$  should have full column rank. Note that it is always possible to represent any transformed code (any nesting) with at most  $2m_S^* + 1$  rows, where  $m_S^* = \max_{S \in \mathbf{S}} m_S$ .

Composition of simpler transformations. Multi-dimensional affine functions capture a sequence of simpler transformations that include permutation, skewing,

```

for (i=0; i< n; i++) {

for (j=0; j< n; j++) {

for (k=0; k< n; k++) {

for (t0=0;t0 \le N-1;t0++) {

S1: C[i,j] = C[i,j] + A[i,k] * B[k,j]; for (t1=0;t1 \le N-1;t1++) {

for (t3=0;t3 \le N-1;t3++) {

C[t1,t0]=A[t1,t3]*B[t3,t0]+C[t1,t0];

for (i=0; i< n; i++) {

for (t3=0;t3 \le N-1;t3++) {

D[t3,t0]=E[t3,t1]*C[t1,t0]+D[t3,t0];

for (j=0; j< n; j++) {

for (k=0; k< n; k++) {

S2: D[i,j] = D[i,j] + E[i,k] * C[k,j];

Transformed code

}

Original code

T_{S_1}(\vec{i}_{S_1}) = \begin{pmatrix} 0 & 1 & 0 \\ 1 & 0 & 0 \\ 0 & 0 & 0 \\ 0 & 0 & 1 \end{pmatrix} \begin{pmatrix} i \\ j \\ k \end{pmatrix} + \begin{pmatrix} 0 \\ 0 \\ 0 \\ 0 \end{pmatrix}

T_{S_2}(\vec{i}_{S_2}) = \begin{pmatrix} 0 & 1 & 0 \\ 0 & 0 & 1 \\ 0 & 0 & 0 \\ 1 & 0 & 0 \end{pmatrix} \begin{pmatrix} i \\ j \\ k \end{pmatrix} + \begin{pmatrix} 0 \\ 0 \\ 1 \\ 0 \end{pmatrix}

i.e.,

\phi_{S_1}^1 = j \quad \phi_{S_2}^1 = j

\phi_{S_1}^2 = i \quad \phi_{S_2}^2 = k

\phi_{S_1}^3 = 0 \quad \phi_{S_2}^3 = 1

\phi_{S_1}^4 = k \quad \phi_{S_2}^4 = i

```

Figure 2.8: Polyhedral transformation: an example

reversal, fusion, fission (distribution), relative shifting, and tiling for fixed tile sizes. Note that tiling cannot be readily expressed as an affine function on the original iterators  $(\vec{i}_S)$ , but can be once supernodes are introduced into the domain increasing its dimensionality: this is covered in detail in a general context in Chapter 5.

Traditional transformations like unimodular transformations [Ban93, Wol95] and non-unimodular [Ram92, LP94, Ram95] ones were applied to a single perfect loop nest in isolation. They are therefore subsumed. Due to the presence of scalar dimensions, polyhedral transformations can be used to represent or transform to any kind of nesting structure. Also, they map iterations of statements to a common multidimensional space providing the ability to interleave iterations of different statements as desired.

One can notice a one-to-one correspondence between the A, B,  $\Gamma$  representation used for URUK/WRAP-IT [GVB<sup>+</sup>06] and the one we described above, except that we have all coefficients in  $\Gamma$  set to zero, i.e., no parametric shifts. The motivation behind this will be clear in the next two chapters. The above representation for transformations was first proposed, though in different forms, by Feautrier [Fea92b] and Kelly et al. [Kel96], but used systematically by viewing it in terms of three components, A, B, and  $\Gamma$  only recently [CGP<sup>+</sup>05, GVB<sup>+</sup>06, Vas07].

The above notation for transformations directly fits with scattering functions that a code generation tool like CLooG [Bas04a, Clo] supports. It refers to  $\mathcal{T}_S$  as a scattering function. On providing the original statement domains,  $\mathcal{D}^S$ , along with  $\mathcal{T}_S$ , Cloog can scan the domains in the global lexicographic ordering imposed by  $T_S(\vec{i}_S)$  across

all  $S \in \mathbf{S}$ . The goal of automatic transformation is to find the unknown coefficients of  $\mathcal{T}_S$ ,  $\forall S \in \mathbf{S}$ .

#### 2.4.1 Why affine transformations?

**Definition 11 (Convex combination).** A convex combination of vectors,  $\vec{x}_1$ ,  $\vec{x}_2$ , ...,  $\vec{x}_n$ , is of the form  $\lambda_1 \vec{x}_1 + \lambda_2 \vec{x}_2 + \cdots + \lambda_n \vec{x}_n$ , where  $\lambda_1, \lambda_2, \ldots, \lambda_n \geq 0$  and  $\sum_{i=1}^n \lambda_i = 1$ .

Informally, a convex combination of two points always lies on the line segment joining the two points. In the general case, a convex combination of any number of points lies inside the convex hull of those points.

The primary reason affine transformations are of interest is that affine transformations are the most general class of transformations that preserve the collinearity and convexity of points in space, besides the ratio of distances. An affine transformation transforms a polyhedron into another polyhedron and one stays in the polyhedral abstraction for further analyses and most importantly for code generation. Code generation is relatively easier and so has been studied extensively for affine transformations. We now quickly show that if  $\mathcal{D}^S$  is convex, its image under the affine function  $\mathcal{T}_S$  is also convex. Let the image be:

$$T(\mathcal{D}^S) = \left\{ \vec{z} \mid \vec{z} = \mathcal{T}_S(\vec{x}), \vec{x} \in \mathcal{D}^S \right\}$$

Consider the convex combination of any two points,  $\mathcal{T}_S(\vec{x})$  and  $\mathcal{T}_S(\vec{y})$ , of  $T(\mathcal{D}^S)$ :

$$\lambda_1 \mathcal{T}_S(\vec{x}) + \lambda_2 \mathcal{T}_S(\vec{y}), \quad \lambda_1 + \lambda_2 = 1, \lambda_1 \ge 0, \lambda_2 \ge 0$$

Now,

$$\lambda_1 \mathcal{T}_S(\vec{x}) + \lambda_2 \mathcal{T}_S(\vec{y}) = \lambda_1 M_S(\vec{x}) + \lambda_1 \vec{t}_S + \lambda_2 M_S(\vec{y}) + \lambda_2 \vec{t}_S$$

$$= M_S(\lambda_1 \vec{x} + \lambda_2 \vec{y}) + \vec{t}_S, \quad (\because \lambda_1 + \lambda_2 = 1)$$

$$= \mathcal{T}_S(\lambda_1 \vec{x} + \lambda_2 \vec{y})$$

$$(2.10)$$

Since  $\mathcal{D}^S$  is convex,  $\lambda_1 \vec{x} + \lambda_2 \vec{y} \in \mathcal{D}^S$ . Hence, from (2.10), we have:

$$\lambda_1 \mathcal{T}_S(\vec{x}) + \lambda_2 \mathcal{T}_S(\vec{y}) \in T(\mathcal{D}^S)$$

$\Rightarrow T(\mathcal{D}^S) \text{ is convex}$

If  $M_S$  (the linear part of  $\mathcal{T}_S$ ) has full column rank, i.e., the rank of  $M_S$  is  $m^S$ ,  $\mathcal{T}_S$  is a one-to-one mapping from  $\mathcal{D}^S$  to  $T(\mathcal{D}^S)$ . A point to note when looking at integer spaces instead of rational or real spaces is that not every integer point in the rational domain that encloses  $T(\mathcal{D}^S)$  may have an integer pre-image in  $\mathcal{D}^S$ , for example, transformations that are non-unimodular may create sparse integer polyhedra. This is not a problem since a code generator like Cloog can scan such sparse polyhedra by inserting modulos. Note that just like convexity, affine transformations also preserve the ratio of distances between points. Since integer points in the original domain are equally spaced, they are so in the transformed space too. Techniques for removal of modulos also exist [Vas07]. Hence, no restrictions need be imposed on the affine function  $\mathcal{T}_S$ . Sparse integer polyhedra also correspond to code with non-unit strides. However, these can be represented with an additional dimension as long as the stride is a constant, for eg., as  $\{0 \le i \le n-1, i=2k\}$  for i going from 0 to n-1 with stride

two. However, if one is interested, a more direct representation for integer points in a polyhedron can be used [S.P00, GR07]. The term  $\mathbb{Z}$ -polyhedron is associated with such a representation which is the image of a rational polyhedron under an affine integer lattice. Closure properties with such a representation under various operations including affine image and pre-image have been proved [GR07].

### 2.5 Putting the Notation Together

Let us put together the notation introduced so far. Let the statements of the program be  $S_1, S_2, \ldots, S_m$ . Let **S** be the set of all statements. Let  $\vec{n}$  be the vector of program parameters, i.e., typically loop bounds or symbols appearing in the loop bounds, access functions, or the statement body.

Let G = (V, E) be the data dependence graph of the original program, i.e.,  $V = \mathbf{S}$  and E is the set of data dependence edges.  $e^{S_i \to S_j} \in E$  denotes an edge from  $S_i$  to  $S_j$ , but we will often drop the superscript on e. For every edge  $e \in E$  from  $S_i$  to  $S_j$ , let the dependence polyhedron be  $\mathcal{P}_e$ , the fact that a source iterations  $\vec{s} \in \mathcal{D}^{S_i}$  and a target iteration  $\vec{t} \in \mathcal{D}^{S_j}$  are dependent are known through the equalities and inequalities in the dependence polyhedron, and we express this fact by:

$$\langle \vec{s}, \vec{t} \rangle \in \mathcal{P}_e \quad \iff \quad \vec{s} \in \mathcal{D}^{S_i}, \vec{t} \in \mathcal{D}^{S_j} \text{ are dependent through edge } e^{S_i \to S_j} \in E$$

$$(2.11)$$

$\phi_{S_i}^k$  denotes the affine hyperplane or function for level k for  $S_i$ ,  $1 \le k \le d$ . The set of all  $\phi_{S_i}^k$ , for  $S_i \in \mathbf{S}$  represent the interleaving of all statement instances at level k.  $\mathcal{T}_S$  is a d-dimensional affine function for each S as defined in (2.9). The subscript

on  $\phi^k$  is dropped when referring to the property of the function across all statements, since all statements instances are mapping to a target space-time with dimensions  $\phi^1, \phi^2, \dots, \phi^d$ .

#### 2.6 Legality and Parallelism

**Dependence satisfaction.** A dependence edge e with polyhedron  $\mathcal{P}_e$  is satisfied at a level l iff l is the first level at which the following condition is met:

$$\forall k (1 \leq k \leq l-1) : \phi_{S_i}^k\left(\vec{t}\right) - \phi_{S_i}^k\left(\vec{s}\right) \geq 0 \quad \land \quad \phi_{S_i}^l\left(\vec{t}\right) - \phi_{S_i}^l\left(\vec{s}\right) \geq 1, \quad \langle \vec{s}, \vec{t} \rangle \in \mathcal{P}_e$$

**Legality.** Statement-wise affine transformations  $(\mathcal{T}_S)$  as defined in (2.9) are legal iff

$$T_{S_i}(\vec{t}) - T_{S_i}(\vec{s}) \succ \vec{0}_d, \quad \langle \vec{s}, \vec{t} \rangle \in \mathcal{P}_e, \forall e \in E$$

(2.12)

**Definition 12** (Permutable band). The  $\phi$ s at levels p, p + 1, ..., p + s - 1 form a permutable band of loops in the transformed space iff

$$\forall k \ (p \le k \le p + s - 1): \quad \phi_{S_j}^k(\vec{t}) - \phi_{S_i}^k(\vec{s}) \ge 0, \quad \langle \vec{s}, \vec{t} \rangle \in \mathcal{P}_e, e \in E_p$$

(2.13)

where  $E_p$  is the set of dependences not satisfied up to level p-1.

The above directly follows from (2.12). Loops within a permutable band can be freely interchanged or permuted among themselves. One can see that doing so will not violate (2.12) since dependence components for all unsatisfied dependences are non-negative at each of the dimensions in the band. We will later find the above definition a little conservative. Its refinement and associated intricacies will be discussed in Section 5.4.2 of Chapter 5.

**Definition 13** (Outer parallel). A  $\{\phi_{S1}, \phi_{S2}, \dots, \phi_{S_m}\}$  is an outer parallel hyperplane if and only if

$$\phi_{S_i}(\vec{t}) - \phi_{S_i}(\vec{s}) = 0, \quad \langle \vec{s}, \vec{t} \rangle \in \mathcal{P}_e, \quad \forall e \in E$$

Outer parallelism is also often referred to as communication-free parallelism or synchronization-free parallelism.

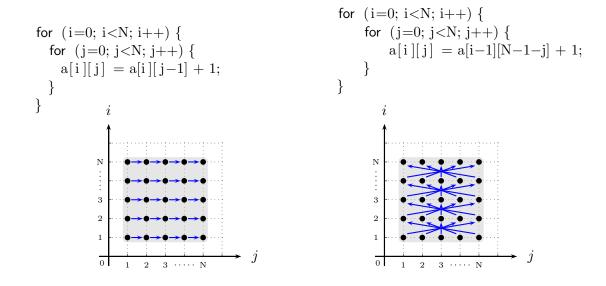

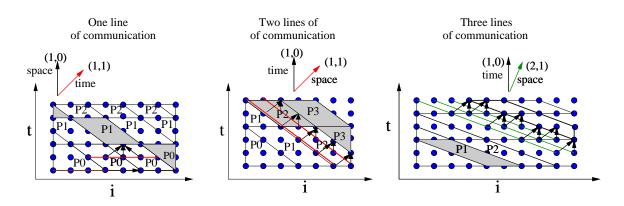

Figure 2.9: Outer parallel loop, i: hy- Figure 2.10: Inner parallel loop, j: hyperplane (1,0) perplane (0,1)

**Definition 14** (Inner parallel). A  $\{\phi_{S1}^k, \phi_{S2}^k, \dots, \phi_{S_m}^k\}$  is an inner parallel hyperplane if and only if  $\phi_{S_i}^k(\vec{t}) - \phi_{S_i}^k(\vec{s}) = 0$ , for every  $\langle \vec{s}, \vec{t} \rangle \in \mathcal{P}_e$ ,  $e \in E_k$ , where  $E_k$  is the set of dependences not satisfied up to level k-1.

It is illegal to move an inner parallel loop in the outer direction since the dependences satisfied at loops it has been moved across may be violated at the new position of the moved loop. However, it is always legal to move an inner parallel loop further inside.

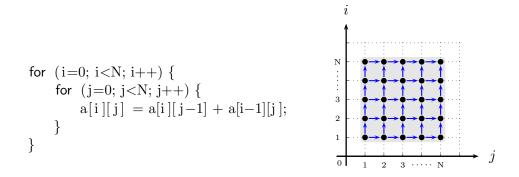

Figure 2.11: Pipelined parallel loop: i or j

Outer and inner parallelism is often referred to as doall parallelism. However, note that inner parallelism requires synchronization every iteration outer to the loop.

Pipelined parallelism. Two or more loops may have dependences that have dependence components along each of them can still be executed in parallel if one of them can be delayed with respect to the other by a fixed amount. If dependence components are non-negative along each of the dimensions in question, one just needs a delay of one. Figure 2.11 shows a code with dependences along both i and j. However, say along i, successive iterations can start with a delay of one and continue executing iterations for j's in sequence. Similarly, if there are n independent dimensions, at most n-1 of them can be pipelined while iterations along at least one will

be executed in sequence. Pipelined parallelism is also often referred to as doacross parallelism. We will formalize conditions for this in a very general setting in Chapter 3 since it is goes together with tiling. Code generation for pipelined parallelism is discussed in Chapter 5.

Space-time mapping. Once properties of each row of  $\mathcal{T}_S$  are known, some of them can be marked as space, i.e., a dimension along which iterations are executed by different processors, while others can be marked as time, i.e., a dimension that is executed sequentially by a single processor. Hence,  $\mathcal{T}_S$  specifies a complete space-time mapping for S. Each of the d dimensions is either space or time. Since  $M_S$  is of full column rank, when an iteration executes and where it executes, is known. However, in reality, post-processing can be done to  $\mathcal{T}_S$  before such a mapping is achieved.

### **CHAPTER 3**

## Automatic Transformations for Parallelism and Locality

The three major phases of an optimizer for parallelism and locality are:

- 1. Static analysis: Computing affine dependences for an input source program

- 2. Automatic transformation: Computing the transformations automatically

- 3. Code generation: Generating the new nested loop code under the computed transformations

As explained in Chapter 1, the first and last steps are currently quite stable, while no scalable and practical approach exists for the middle step that works for all polyhedral input or for input that the first and last steps are known to be quite advanced for. This chapter deals with the theory for the key middle step: automatic transformation, which is often considered synonymous with automatic parallelization.

## 3.1 Schedules, Allocations, and Partitions

Hyperplanes can be interpreted as schedules, allocations, or partitions, or any other term a researcher may define based on the properties it satisfies. Saying that a hyperplane is one of them implies a particular property that the new loop will satisfy in the transformed space. Based on the properties the hyperplanes will satisfy at various levels, certain further transformations like tiling, unroll-jamming, or marking it parallel, can be performed. Typically, scheduling-based works [Fea92a, Fea92b, DR96, Gri04] obtains the new set of hyperplanes as schedules and allocations, while Lim and Lam [LL98] find them as space and time partitions.

### 3.2 Limitations of Previous Techniques